# Keysight D9040USBC USB4 Compliance Test Application

# **Notices**

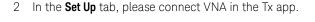

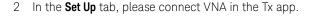

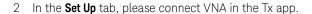

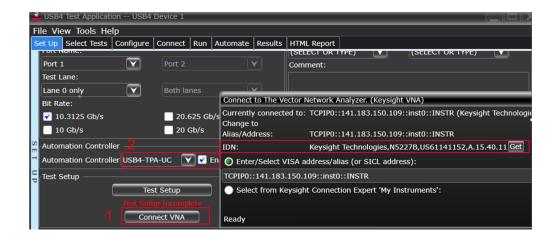

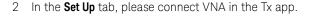

#### © Keysight Technologies 2024

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

#### **Trademarks**

UNIX is a registered trademark of UNIX System Laboratories in the U.S.A. and other countries. Target is copyrighted by Thru-Put Systems, Inc.

#### Version

Version 1.30.0.0

#### Edition

January 2024

Available in electronic format only

Keysight Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

# Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE

TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

# **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

# U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no

greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

# Safety Notices

#### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

# WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# Contents

# 1 Overview

| USB4 Automated Testing—At a Glan               | ce         | 30 |

|------------------------------------------------|------------|----|

| Required Equipment and Software                | 31         |    |

| Hardware 31<br>Software 34                     |            |    |

| Licensing information 35                       |            |    |

| In This Book 36                                |            |    |

| See Also 36                                    |            |    |

| References 36                                  |            |    |

| 2 Installing the Test Application and Licenses |            |    |

| Installing the Test Application 38             |            |    |

| Installing the License Key 39                  |            |    |

| Using Keysight License Manager 5               | 39         |    |

| Using Keysight License Manager 6               | 40         |    |

| 3 Preparing to Take Measurements               |            |    |

| Calibrating the Oscilloscope 44                |            |    |

| Starting the USB4 Test Application             | 45         |    |

| Setting up the USB4 Test Applicatio            | <b>n</b> 4 | 8  |

| Calibration Setup for Compliance Te            | sts        | 56 |

| Channel Skew Calibration 56                    |            |    |

| Preset Calibration 60  Power Profile 62        |            |    |

| Fixture and Cable De-Embed 63                  |            |    |

|                                                |            |    |

| 4 Host / Device USB4 Transmitter Testing       |            |    |

| Architectural Overview 66                      |            |    |

| Overview 66                                    |            |    |

| USB4 System Description 66                     |            |    |

# **USB4 Electrical Compliance Methodology** 68

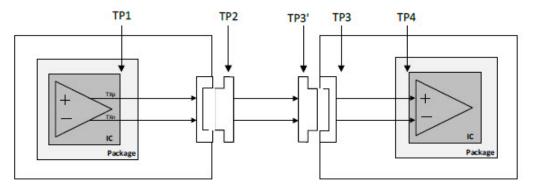

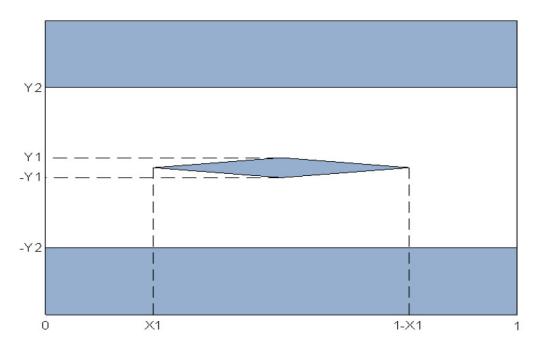

System Compliance Test Point Definitions 68

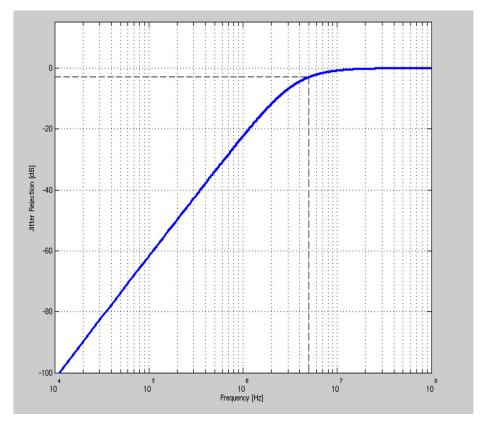

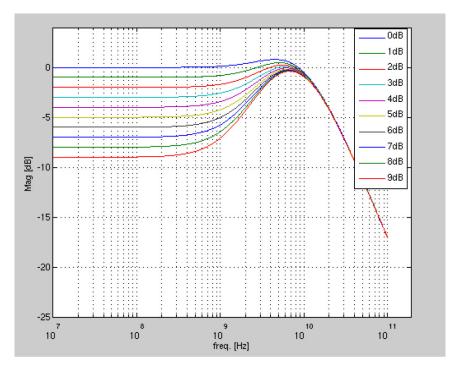

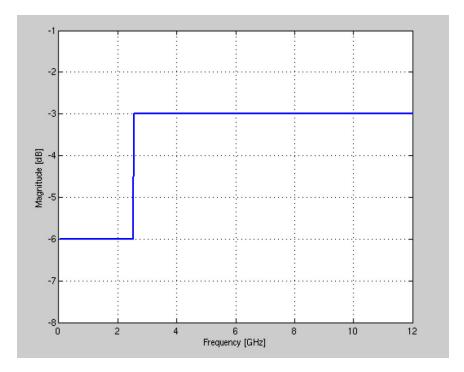

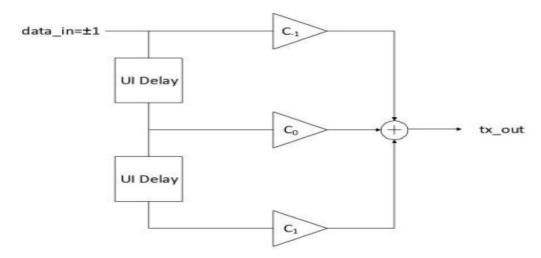

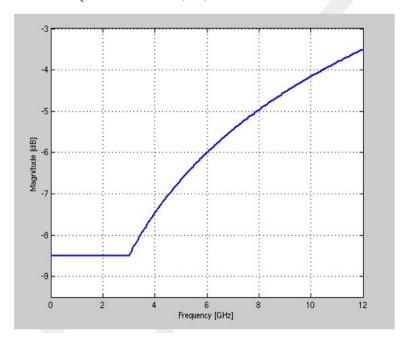

Reference Clock-and-Data-Recovery (CDR) Function 69

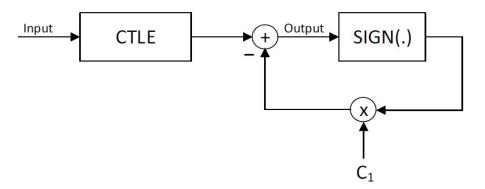

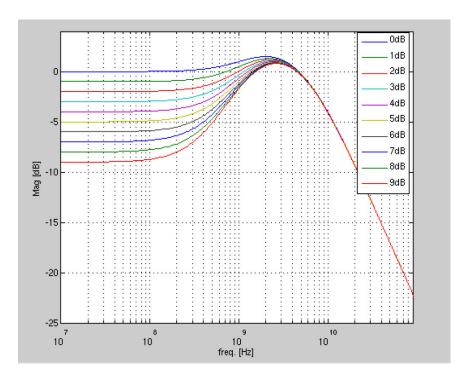

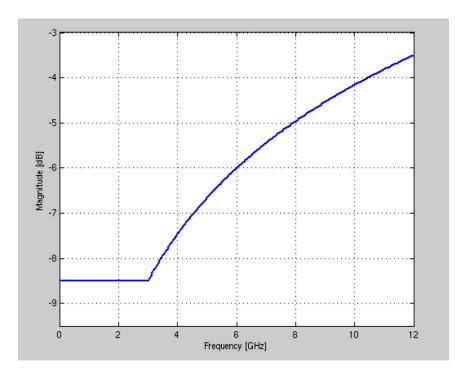

Reference Equalization Function 70

# **Router Assembly Transmitter Compliance** 73

Transmitter Specifications Applied for All Speeds 73

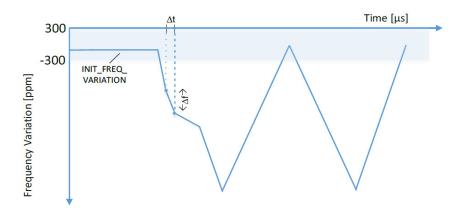

Transmitter Frequency Variations during Link Training 76

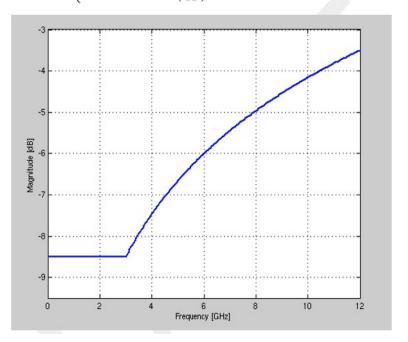

Transmitter Differential Return Loss 78

Transmitter Common Mode Return Loss 79

Transmit Equalization 80

Transmitter Compliance Specifications for Gen 2 83

Transmitter Compliance Specifications for Gen 3 Interconnects 85

# 5 Transmitter Tests for 10.3125 GB/s Systems

#### Tx Preset Calibration 91

Test Overview 91

Test Setup 91

Test Procedure 93

Expected / Observable Results 93

Test References 93

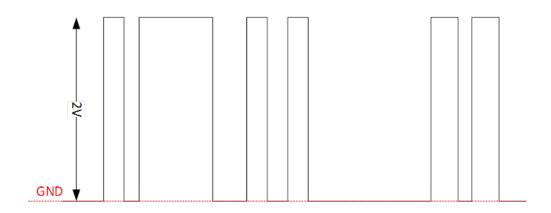

# SBTX High Voltage 94

Test Overview 94

Test Pass Requirement 94

Test Procedure 94

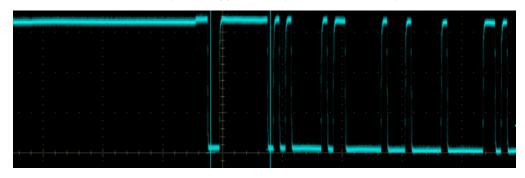

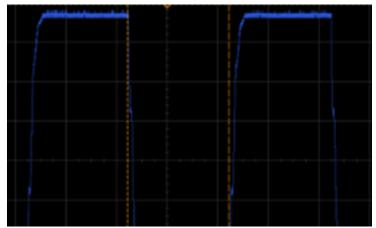

Expected / Observable Results 95

Test References 95

# SBTX Low Voltage 96

Test Overview 96

Test Pass Requirement 96

Test Procedure 96

Expected / Observable Results 97

Test References 97

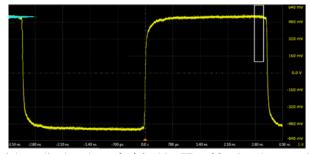

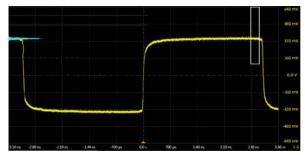

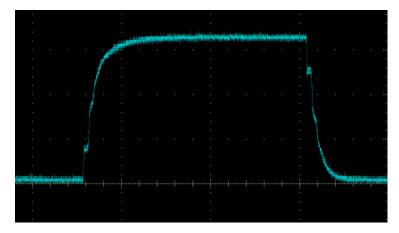

# SBTX Rise/Fall Time 98

Test Overview 98

Test Pass Requirement 98

Test Procedure 99

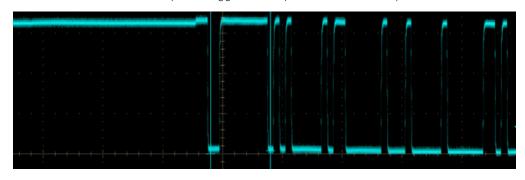

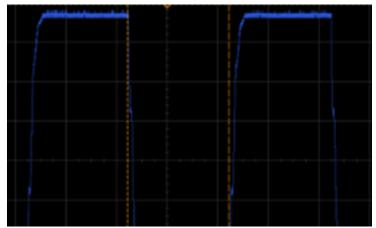

Expected / Observable Results 100

Test References 100

| SBIX UI Duration 101                                                                                                            |      |     |

|---------------------------------------------------------------------------------------------------------------------------------|------|-----|

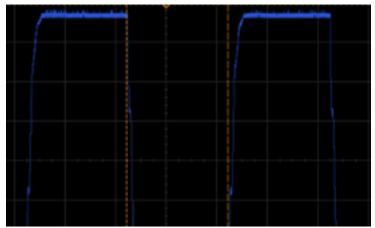

| Test Overview 101 Test Pass Requirement 101 Test Procedure 102 Expected / Observable Results                                    | 102  |     |

| Test References 103                                                                                                             | 100  |     |

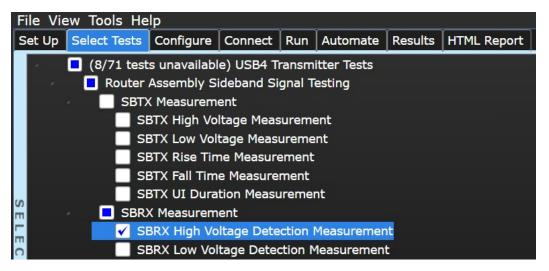

| SBRX High Voltage Detection                                                                                                     | 104  |     |

| Test Overview 104 Test Pass Requirement 104 Test Procedure 105                                                                  |      |     |

| Expected / Observable Results<br>Test References 105                                                                            | 105  |     |

| SBRX Low Voltage Detection                                                                                                      | 106  |     |

| Test Overview 106 Test Pass Requirement 106 Test Procedure 106 Expected / Observable Results Test References 106                | 106  |     |

| TX Rise/Fall Time 107                                                                                                           |      |     |

| Test Overview 107 Test Pass Requirement 107 Test Setup 107 Test Procedure 108 Expected / Observable Results Test References 108 | 108  |     |

| <b>Tx Uncorrelated Jitter</b> 109                                                                                               |      |     |

| Test Overview 109 Test Pass Requirement 109 Test Setup 109 Test Procedure 110                                                   |      |     |

| Expected / Observable Results Test References 110                                                                               | 110  |     |

| Tx Uncorrelated Deterministic Ji                                                                                                | tter | 111 |

| Test Overview 111 Test Pass Requirement 111 Test Setup 111 Test Procedure 112                                                   |      |     |

| Expected / Observable Results Test References 112                                                                               | 112  |     |

| Tx Data Dependent Jitter 113  Test Overview 113  Test Pass Requirement 113  Test Setup 113  Test Procedure 114  Expected / Observable Results 114  Tx Duty Cycle Distortion 115  Test Pass Requirement 115  Test Pass Requirement 115  Test Setup 115  Test Procedure 116  Expected / Observable Results 116  Test References 116  Tx Low Frequency Uncorrelated Deterministic Jitter 117  Test Pass Requirement 117  Test Pass Requirement 117  Test Setup 117  Test Setup 117  Test Procedure 118  Expected / Observable Results 118  Test References 118 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Pass Requirement 113 Test Setup 113 Test Procedure 114 Expected / Observable Results 114 Test References 114  Tx Duty Cycle Distortion 115 Test Overview 115 Test Pass Requirement 115 Test Procedure 116 Expected / Observable Results 116 Test References 116  Tx Low Frequency Uncorrelated Deterministic Jitter 117 Test Pass Requirement 117 Test Pass Requirement 117 Test Pass Requirement 117 Test Setup 117 Test Procedure 118 Expected / Observable Results 118                                                                              |

| Test Overview 115 Test Pass Requirement 115 Test Setup 115 Test Procedure 116 Expected / Observable Results 116 Test References 116  Tx Low Frequency Uncorrelated Deterministic Jitter 117 Test Overview 117 Test Pass Requirement 117 Test Setup 117 Test Procedure 118 Expected / Observable Results 118                                                                                                                                                                                                                                                 |

| Test Pass Requirement 115 Test Setup 115 Test Procedure 116 Expected / Observable Results 116 Test References 116  Tx Low Frequency Uncorrelated Deterministic Jitter 117 Test Overview 117 Test Pass Requirement 117 Test Setup 117 Test Procedure 118 Expected / Observable Results 118                                                                                                                                                                                                                                                                   |

| Test References 116  Tx Low Frequency Uncorrelated Deterministic Jitter 117 Test Overview 117 Test Pass Requirement 117 Test Setup 117 Test Procedure 118 Expected / Observable Results 118                                                                                                                                                                                                                                                                                                                                                                 |

| Tx Low Frequency Uncorrelated Deterministic Jitter  Test Overview 117  Test Pass Requirement 117  Test Setup 117  Test Procedure 118  Expected / Observable Results 118                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Tx Total Jitter 119  Test Overview 119  Test Pass Requirement 119  Test Setup 119  Test Procedure 120  Expected / Observable Results 120  Test References 120                                                                                                                                                                                                                                                                                                                                                                                               |

| Tx Uncorrelated Jitter TP3 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Test Overview 121 Test Pass Requirement 121 Test Setup 121 Test Procedure 122 Expected / Observable Results 122                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Tx Uncorrelated Deterministic J                                                                                                 | itter TP3       | 123 |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|

| Test Overview 123 Test Pass Requirement 123 Test Setup 123 Test Procedure 124 Expected / Observable Results Test References 124 | 124             |     |

| <b>Tx Total Jitter TP3</b> 125                                                                                                  |                 |     |

| Test Overview 125 Test Pass Requirement 125 Test Setup 125 Test Procedure 126 Expected / Observable Results Test References 127 | 126             |     |

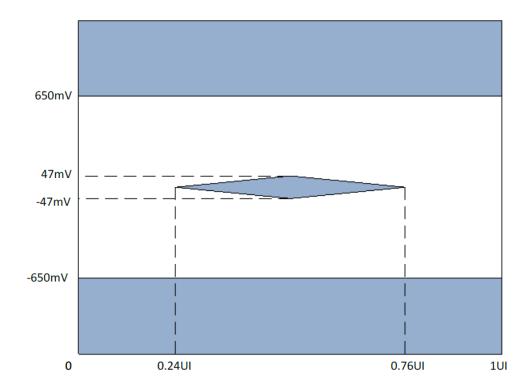

| Tx Eye Diagram TP3 128                                                                                                          |                 |     |

| Test Overview 128 Test Pass Requirement 128 Test Setup 129 Test Procedure 130                                                   | 100             |     |

| Expected / Observable Results Test References 130                                                                               | 130             |     |

| Tx Average Unit Interval, Min/Ma                                                                                                | <b>ax</b> 131   |     |

| Test Overview 131 Test Pass Requirement 131 Test Setup 131 Test Procedure 132                                                   |                 |     |

| Expected / Observable Results Test References 132                                                                               | 132             |     |

| Tx Minimum Unit Interval, Min/N                                                                                                 | <b>/lax</b> 133 |     |

| Test Overview 133 Test Pass Requirement 133 Test Setup 133 Test Procedure 134                                                   |                 |     |

| Expected / Observable Results                                                                                                   | 134             |     |

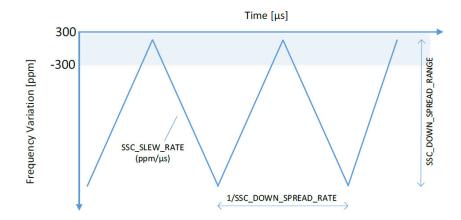

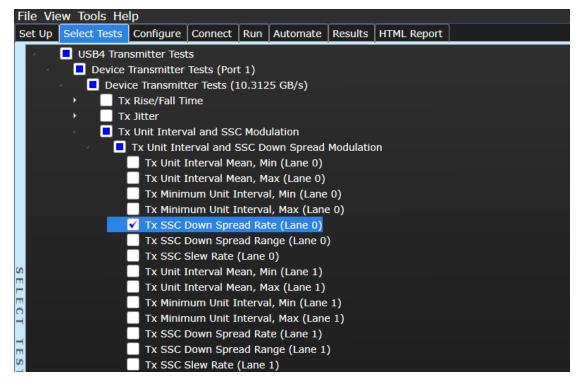

# **Tx SSC Down Spread Rate** 135

Test Overview 135

Test Pass Requirement 135

Test Setup 135

Test Procedure 136

Expected / Observable Results 136

Test References 136

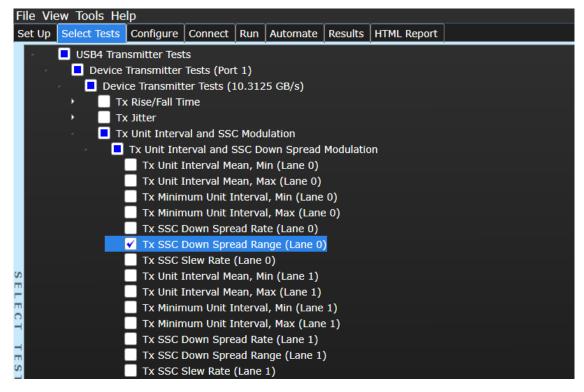

# Tx SSC Down Spread Range 137

Test Overview 137

Test Pass Requirement 137

Test Setup 137

Test Procedure 138

Expected / Observable Results 138

Test References 138

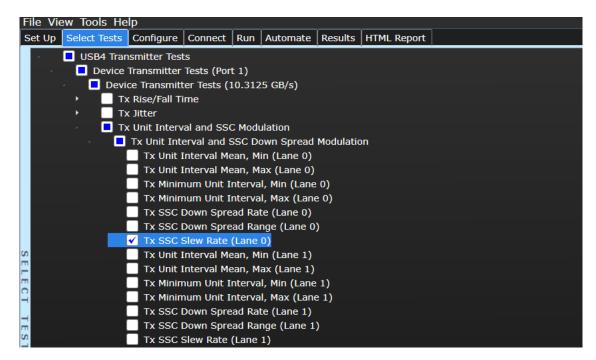

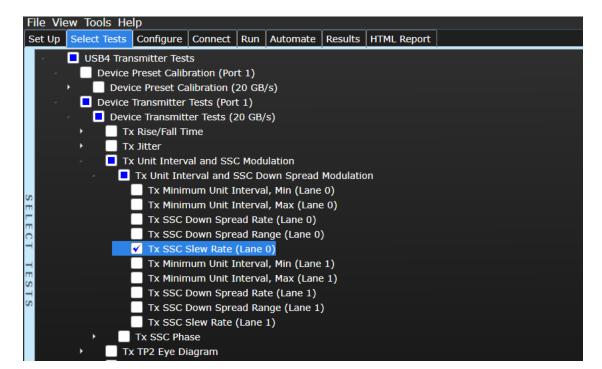

# Tx SSC Slew Rate 139

Test Overview 139

Test Pass Requirement 139

Test Setup 139

Test Procedure 140

Expected / Observable Results 140

Test References 140

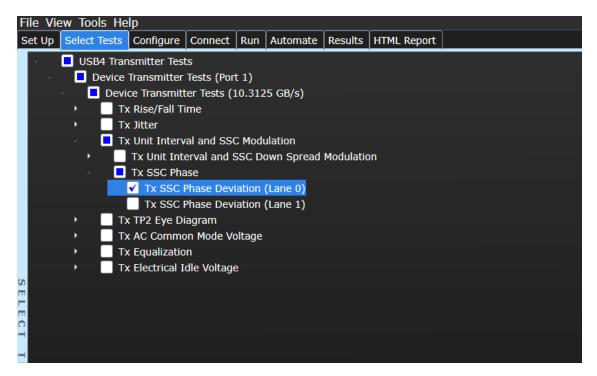

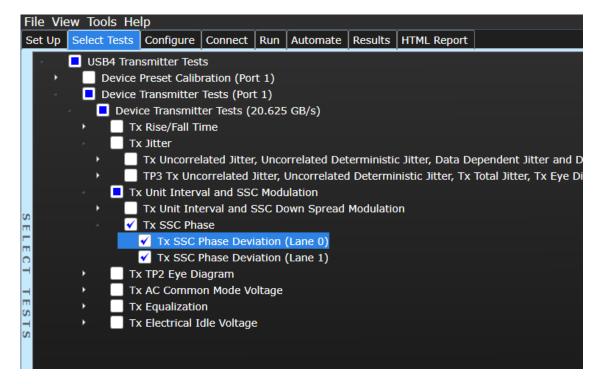

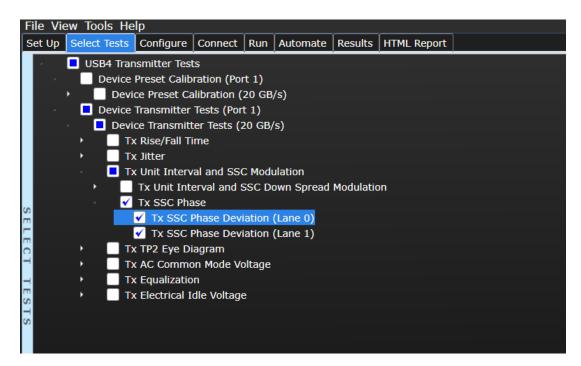

# Tx SSC Phase Deviation 141

Test Overview 141

Test Pass Requirement 141

Test Setup 141

Test Procedure 142

Expected / Observable Results 142

Test References 142

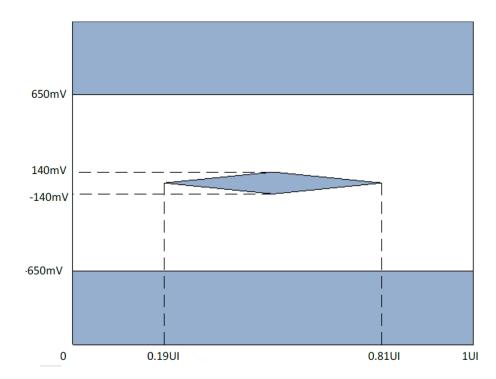

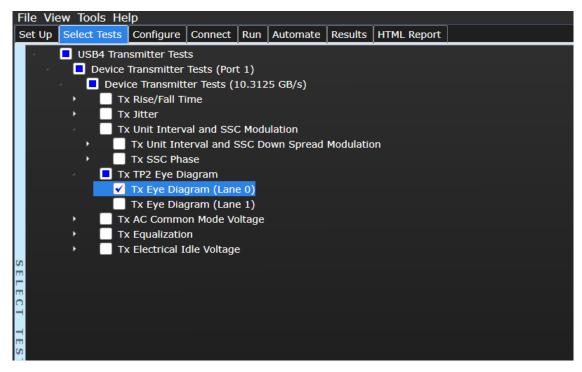

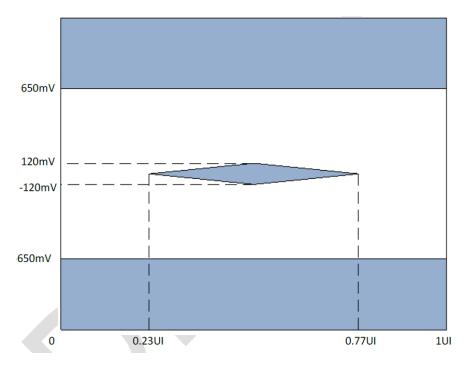

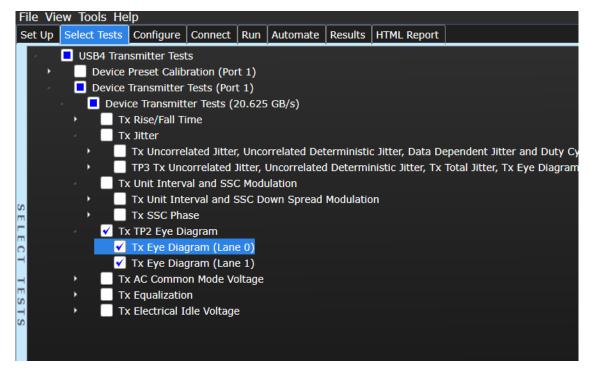

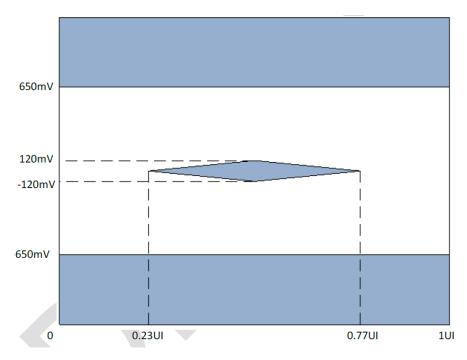

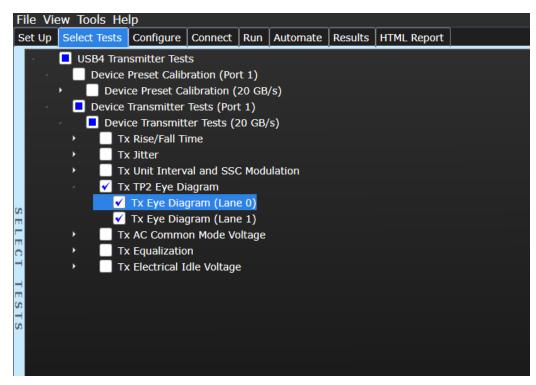

# Tx Eye Diagram 143

Test Overview 143

Test Pass Requirement 143

Test Setup 143

Test Procedure 144

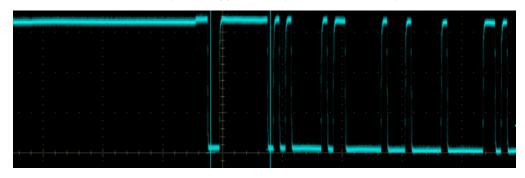

Expected / Observable Results 144

|      | Test Overview 146 Test Pass Requirement 146 Test Setup 146 Test Procedure 147 Expected / Observable Results Test References 147 | 147            |

|------|---------------------------------------------------------------------------------------------------------------------------------|----------------|

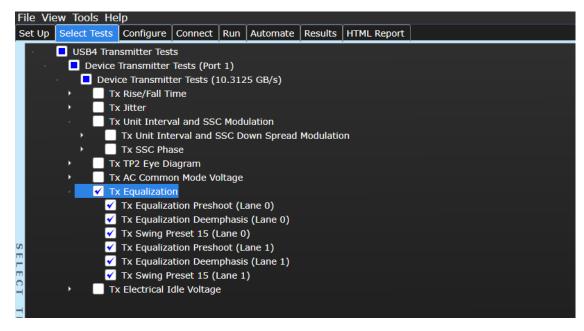

| Tx E | Equalization Tests 148                                                                                                          |                |

|      | Test Overview 148 Test Pass Requirement 148 Test Setup 149 Test Procedure 151                                                   |                |

|      | Expected / Observable Results Test References 153                                                                               | 153            |

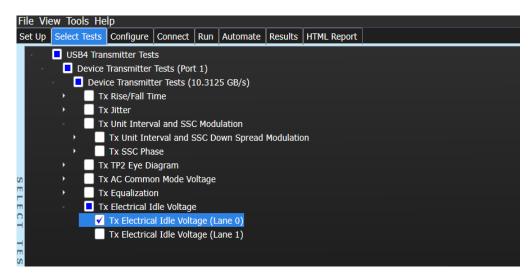

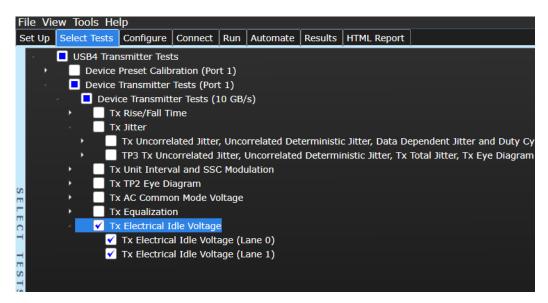

| Tx E | Electrical Idle Voltage Test                                                                                                    | 154            |

|      | Test Overview 154 Test Pass Requirement 154 Test Setup 154 Test Procedure 155 Measurement Procedure 155                         |                |

|      | Expected / Observable Results Test References 155                                                                               | 155            |

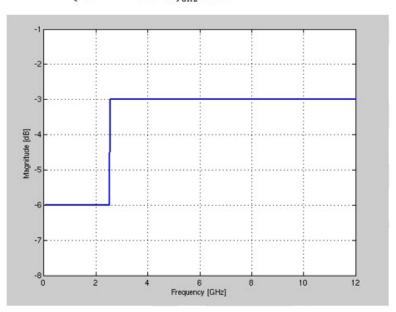

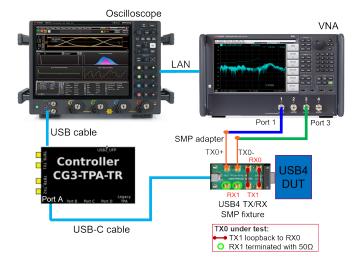

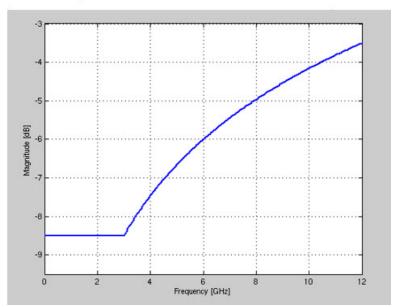

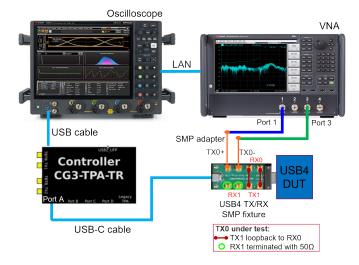

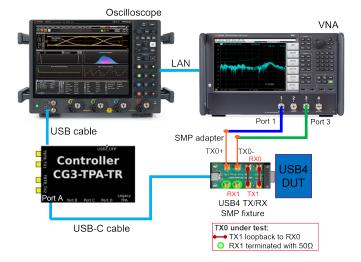

| Tx C | Differential Return Loss Test                                                                                                   | 156            |

|      | Test Overview 156 Test Pass Requirement 156 Test Setup 157 Test Procedure 160 Expected / Observable Results Test References 160 | 160            |

| Tx C | Common Mode Return Loss Te                                                                                                      | <b>est</b> 16° |

|      | Test Overview 161 Test Pass Requirement 161 Test Setup 162 Test Procedure 165                                                   |                |

|      | Expected / Observable Results Test References 165                                                                               | 165            |

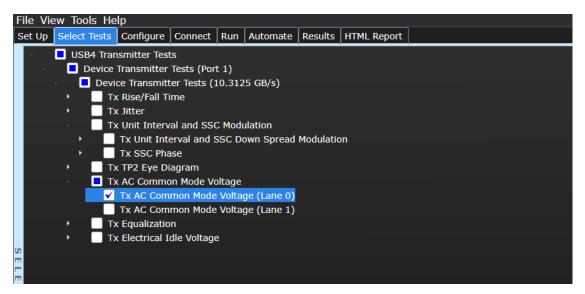

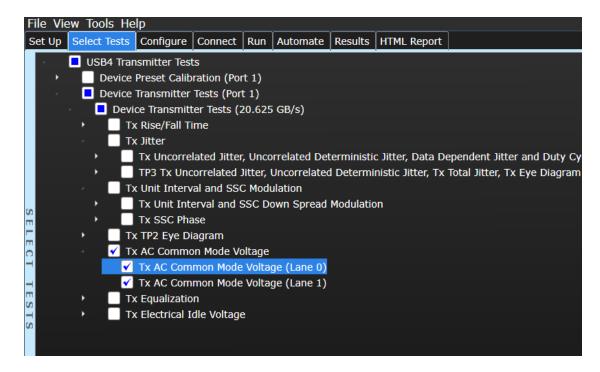

**Tx AC Common Mode Voltage** 146

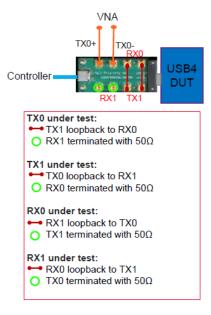

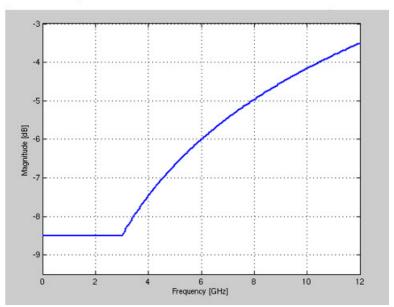

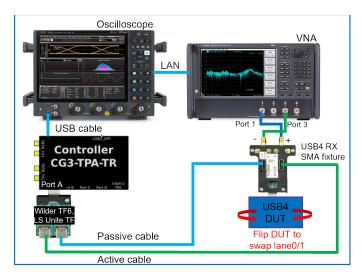

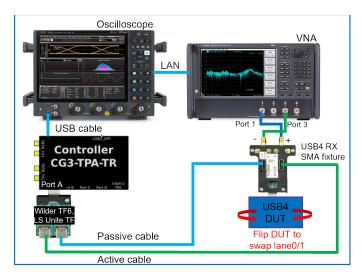

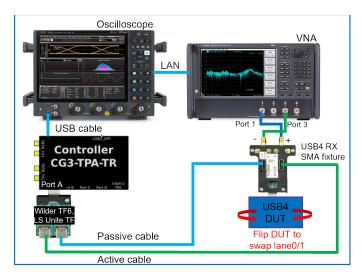

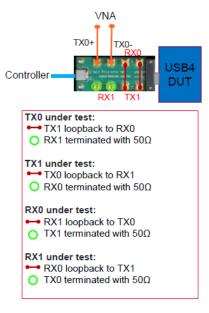

# **Rx Differential Return Loss Test** 166

Test Overview 166

Test Pass Requirement 166

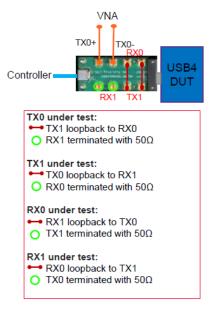

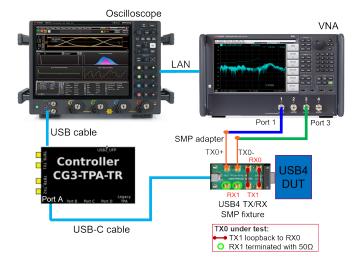

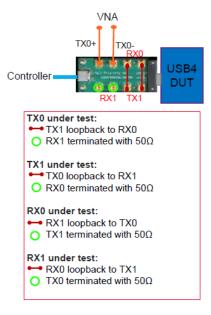

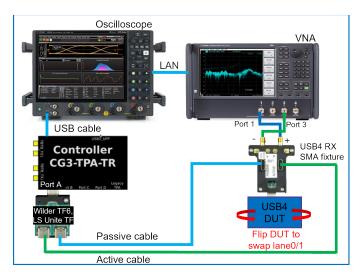

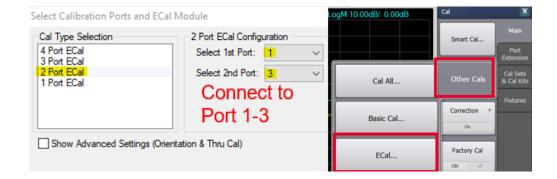

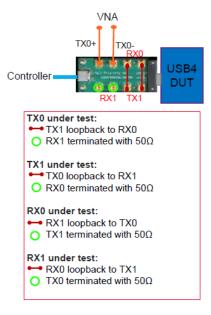

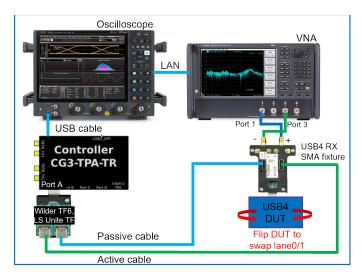

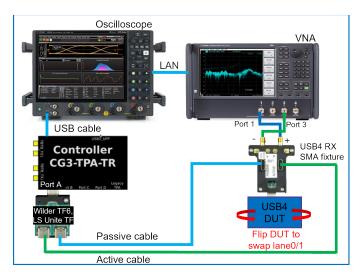

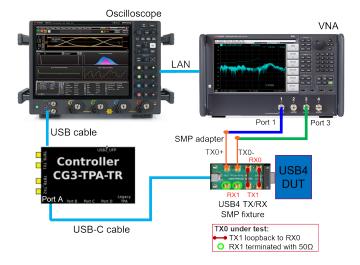

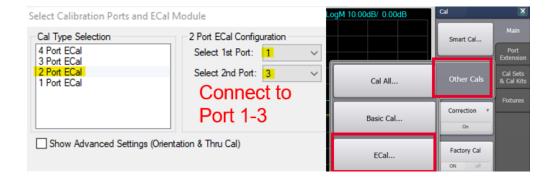

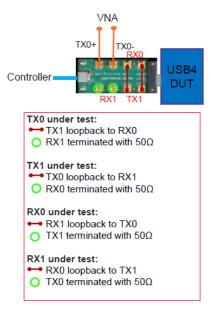

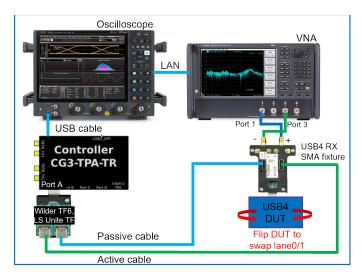

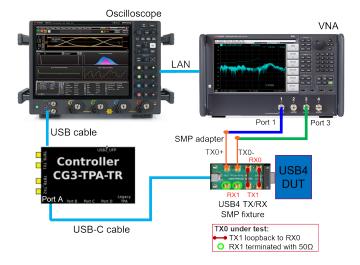

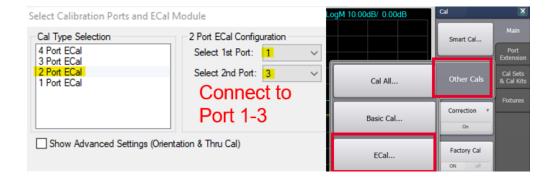

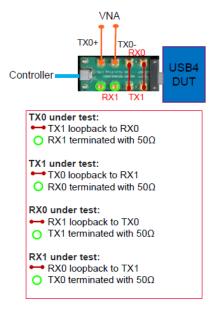

Test Setup 167

Test Procedure 170

Expected / Observable Results 170

Test References 170

# Rx Common Mode Return Loss Test 171

Test Overview 171

Test Pass Requirement 171

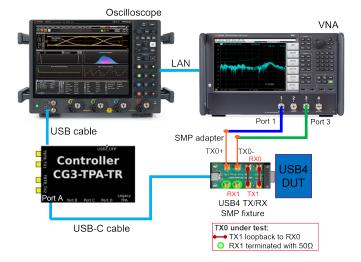

Test Setup 172

Test Procedure 175

Expected / Observable Results 175

Test References 175

# 6 Transmitter Tests for 10 GB/s Systems

# Tx Preset Calibration 178

Test Overview 178

Test Setup 178

Test Procedure 181

Expected / Observable Results 181

Test References 181

# SBTX High Voltage 182

Test Overview 182

Test Pass Requirement 182

Test Procedure 182

Expected / Observable Results 183

Test References 183

# SBTX Low Voltage 184

Test Overview 184

Test Pass Requirement 184

Test Procedure 184

Expected / Observable Results 185

Test References 185

#### SBTX Rise/Fall Time 186

Test Overview 186

Test Pass Requirement 186

Test Procedure 187

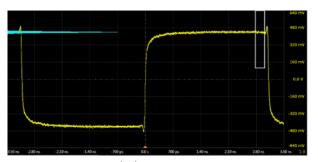

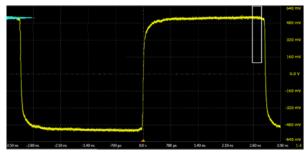

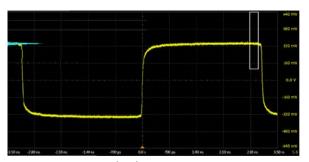

Expected / Observable Results 188

| Test Pass Requirement 189 Test Procedure 190                                  |        |     |

|-------------------------------------------------------------------------------|--------|-----|

| Expected / Observable Results Test References 191                             | 191    |     |

| SBRX High Voltage Detection                                                   | 192    |     |

| Test Overview 192 Test Pass Requirement 192 Test Procedure 193                |        |     |

| Expected / Observable Results Test References 193                             | 193    |     |

| SBRX Low Voltage Detection                                                    | 194    |     |

| Test Overview 194 Test Pass Requirement 194 Test Procedure 194                |        |     |

| Expected / Observable Results Test References 194                             | 194    |     |

| Tx Rise/Fall Time 195                                                         |        |     |

| Test Overview 195 Test Pass Requirement 195 Test Setup 195 Test Procedure 196 |        |     |

| Expected / Observable Results Test References 196                             | 196    |     |

| Tx Uncorrelated Jitter 197                                                    |        |     |

| Test Overview 197 Test Pass Requirement 197 Test Setup 197                    |        |     |

| Test Procedure 198 Expected / Observable Results Test References 198          | 198    |     |

| Tx Uncorrelated Deterministic J                                               | litter | 199 |

| Test Overview 199 Test Pass Requirement 199 Test Setup 199 Test Procedure 200 |        |     |

| Expected / Observable Results Test References 200                             | 200    |     |

**SBTX UI Duration** 189

# Tx Data Dependent Jitter 201

Test Overview 201

Test Pass Requirement 201

Test Setup 201

Test Procedure 202

Expected / Observable Results 202

Test References 202

# Tx Duty Cycle Distortion 203

Test Overview 203

Test Pass Requirement 203

Test Setup 203

Test Procedure 204

Expected / Observable Results 204

Test References 204

# Tx Low Frequency Uncorrelated Deterministic Jitter 205

Test Overview 205

Test Pass Requirement 205

Test Setup 205

Test Procedure 206

Expected / Observable Results 206

Test References 206

# **Tx Total Jitter** 207

Test Overview 207

Test Pass Requirement 207

Test Setup 207

Test Procedure 208

Expected / Observable Results 208

Test References 208

# Tx Uncorrelated Jitter TP3 209

Test Overview 209

Test Pass Requirement 209

Test Setup 209

Test Procedure 210

Expected / Observable Results 210

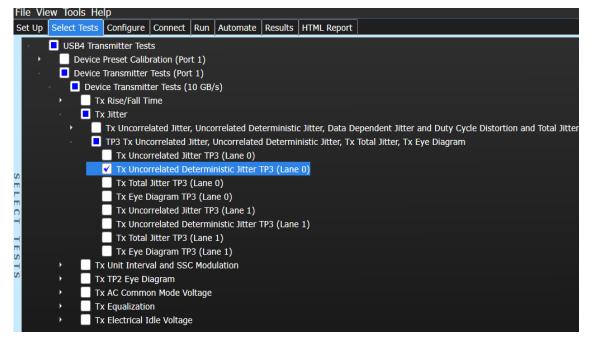

# Tx Uncorrelated Deterministic Jitter TP3 211

Test Overview 211

Test Pass Requirement 211

Test Setup 211

Test Procedure 212

Expected / Observable Results 212

Test References 212

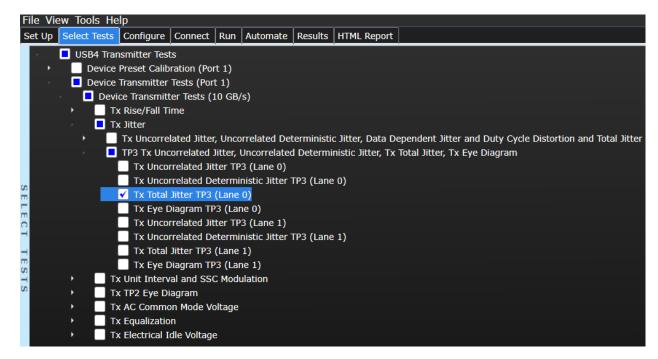

# Tx Total Jitter TP3 213

Test Overview 213

Test Pass Requirement 213

Test Setup 213

Test Procedure 214

Expected / Observable Results 214

Test References 215

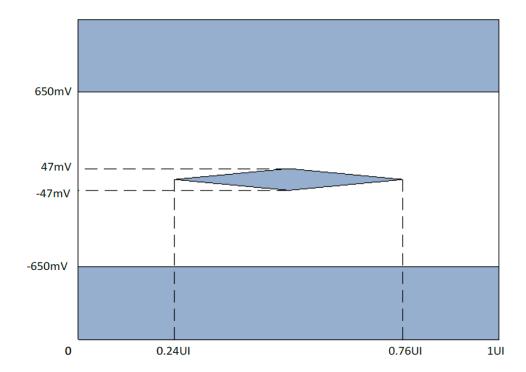

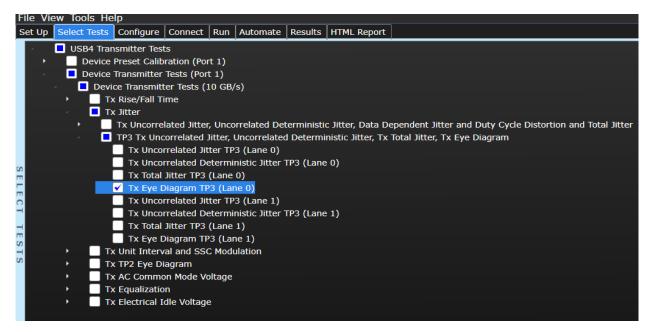

# **Tx Eye Diagram TP3** 216

Test Overview 216

Test Pass Requirement 216

Test Setup 216

Test Procedure 217

Expected / Observable Results 217

Test References 218

# Tx Minimum Unit Interval, Min/Max 219

Test Overview 219

Test Pass Requirement 219

Test Setup 219

Test Procedure 220

Expected / Observable Results 220

Test References 220

# Tx SSC Down Spread Rate 221

Test Overview 221

Test Pass Requirement 221

Test Setup 221

Test Procedure 222

Expected / Observable Results 222

| Test Overview 223 Test Pass Requirement 223 Test Setup 223 Test Procedure 224 Expected / Observable Results Test References 224  Tx SSC Slew Rate 225            | 224 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Test Overview 225 Test Pass Requirement 225 Test Setup 225 Test Procedure 226 Expected / Observable Results Test References 226                                  | 226 |

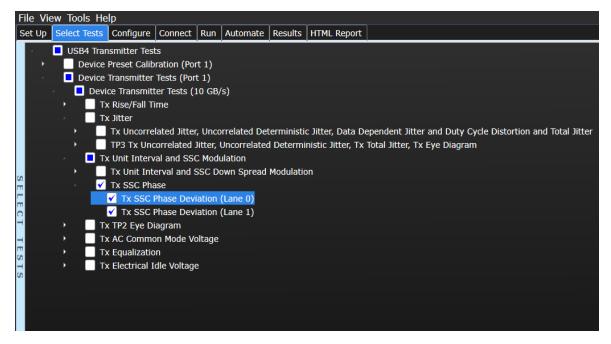

| Tx SSC Phase Deviation 227  Test Overview 227  Test Pass Requirement 227  Test Setup 227  Test Procedure 228  Expected / Observable Results  Test References 228 | 228 |

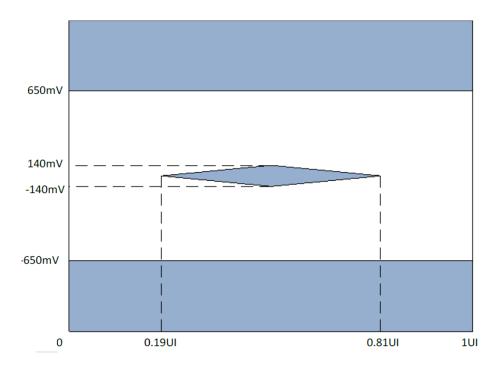

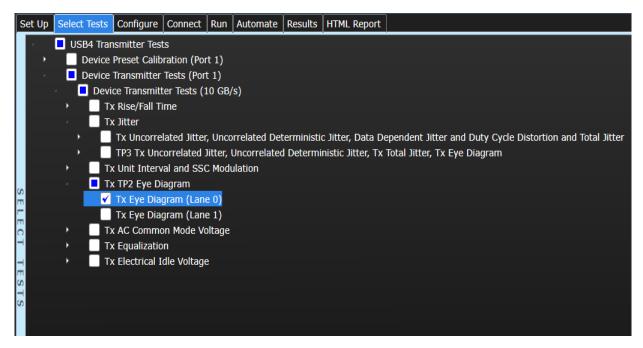

| Tx Eye Diagram 229  Test Overview 229  Test Pass Requirement 229  Test Setup 229  Test Procedure 230  Expected / Observable Results  Test References 230         | 230 |

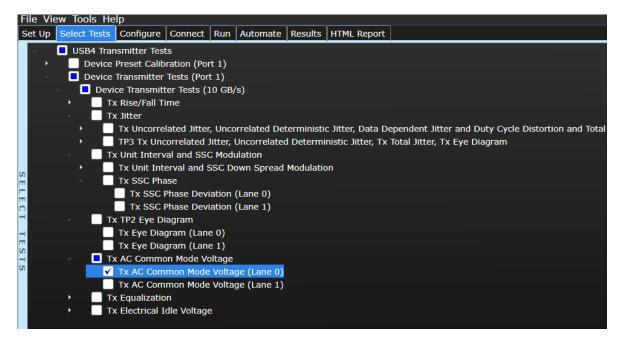

| Tx AC Common Mode Voltage                                                                                                                                        | 231 |

| Test Overview 231 Test Pass Requirement 231 Test Setup 231 Test Procedure 232                                                                                    |     |

| Expected / Observable Results Test References 232                                                                                                                | 232 |

Tx SSC Down Spread Range 223

# Tx Equalization Tests 233 Test Overview 233 Test Pass Requirement 233 Test Setup 234 Test Procedure 235 Expected / Observable Results 237 Test References 237

# Tx Electrical Idle Voltage Test 238

Test Overview 238

Test Pass Requirement 238

Test Setup 238

Test Procedure 239

Measurement Procedure 239

Expected / Observable Results 239

Test References 239

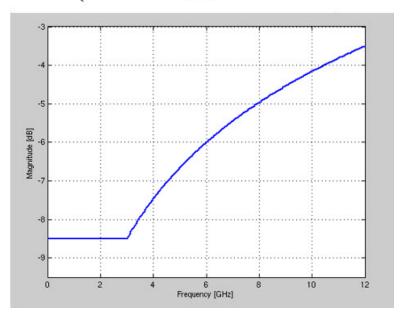

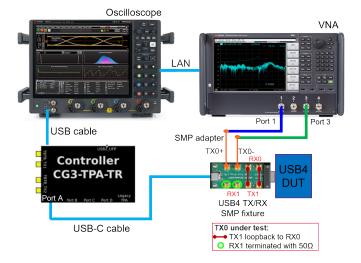

# Tx Differential Return Loss Test 240

Test Overview 240

Test Pass Requirement 240

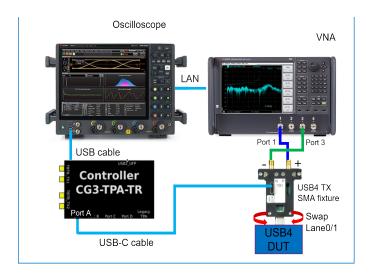

Test Setup 241

Test Procedure 244

Expected / Observable Results 244

Test References 244

# Tx Common Mode Return Loss Test 245

Test Overview 245

Test Pass Requirement 245

Test Setup 246

Test Procedure 249

Expected / Observable Results 249

Test References 249

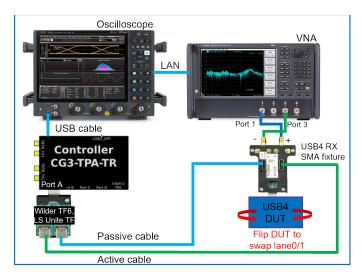

# Rx Differential Return Loss Test 250

Test Overview 250

Test Pass Requirement 250

Test Setup 251

Test Procedure 254

Expected / Observable Results 254

Test References 254

# Rx Common Mode Return Loss Test 255

Test Overview 255

Test Pass Requirement 255

Test Setup 256

Test Procedure 259

Expected / Observable Results 259

Test References 259

# 7 Transmitter Tests for 20.625 GB/s Systems

# **Tx Preset Calibration** 262

Test Overview 262

Test Setup 262

Test Procedure 265

Expected / Observable Results 265

Test References 265

# SBTX High Voltage 266

Test Overview 266

Test Pass Requirement 266

Test Procedure 266

Expected / Observable Results 267

Test References 267

# SBTX Low Voltage 268

Test Overview 268

Test Pass Requirement 268

Test Procedure 268

Expected / Observable Results 269

Test References 269

# SBTX Rise/Fall Time 270

Test Overview 270

Test Pass Requirement 270

Test Procedure 271

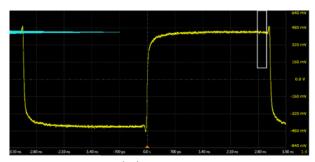

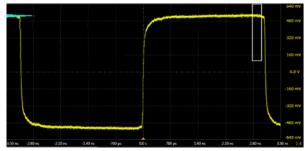

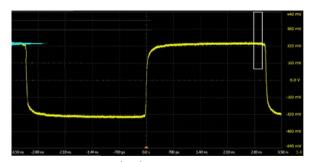

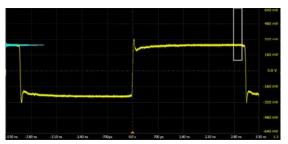

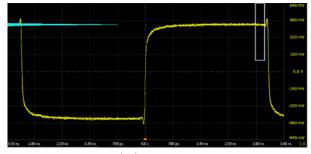

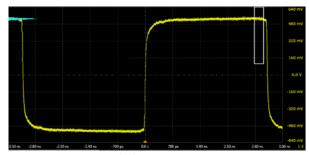

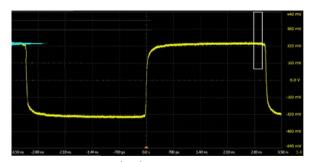

Expected / Observable Results 272

Test References 272

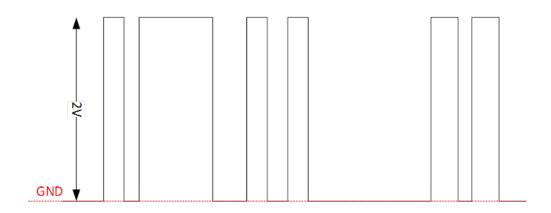

# **SBTX UI Duration** 273

Test Overview 273

Test Pass Requirement 273

Test Procedure 274

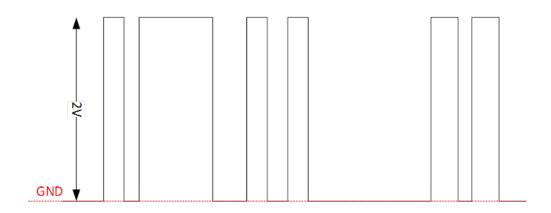

Expected / Observable Results 275

| SBRX High Voltage Detection                                                                                                                                 | 276 |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| Test Overview 276 Test Pass Requirement 276 Test Procedure 277 Expected / Observable Results Test References 277                                            | 277 |     |

| SBRX Low Voltage Detection 2                                                                                                                                | 278 |     |

| Test Overview 278 Test Pass Requirement 278 Test Procedure 278 Expected / Observable Results Test References 278                                            | 278 |     |

| Tx Rise/Fall Time 279  Test Overview 279  Test Pass Requirement 279  Test Setup 279  Test Procedure 280  Expected / Observable Results  Test References 280 | 280 |     |

| Tx Uncorrelated Jitter 281  Test Overview 281  Test Pass Requirement 281  Test Setup 281                                                                    |     |     |

| Test Procedure 282 Expected / Observable Results Test References 282                                                                                        | 282 |     |

| Tx Uncorrelated Deterministic Jit                                                                                                                           | ter | 283 |

| Test Overview 283 Test Pass Requirement 283 Test Setup 283 Test Procedure 284 Expected / Observable Results                                                 | 284 |     |

| Test References 284                                                                                                                                         |     |     |

| Tx Data Dependent Jitter 285  Test Overview 285  Test Pass Requirement 285  Test Setup 285  Test Procedure 286  Expected / Observable Results               | 286 |     |

| Test References 286                                                                                                                                         |     |     |

# **Tx Duty Cycle Distortion** 287

Test Overview 287

Test Pass Requirement 287

Test Setup 287

Test Procedure 288

Expected / Observable Results 288

Test References 288

# Tx Low Frequency Uncorrelated Deterministic Jitter 289

Test Overview 289

Test Pass Requirement 289

Test Setup 289

Test Procedure 290

Expected / Observable Results 290

Test References 290

# Tx Total Jitter 291

Test Overview 291

Test Pass Requirement 291

Test Setup 291

Test Procedure 292

Expected / Observable Results 292

Test References 292

# Tx Uncorrelated Jitter TP3 293

Test Overview 293

Test Pass Requirement 293

Test Setup 293

Test Procedure 294

Expected / Observable Results 294

Test References 294

# Tx Uncorrelated Deterministic Jitter TP3 295

Test Overview 295

Test Pass Requirement 295

Test Setup 295

Test Procedure 296

Expected / Observable Results 296

# **Tx Total Jitter TP3** 297

Test Overview 297

Test Pass Requirement 297

Test Setup 297

Test Procedure 298

Expected / Observable Results 299

Test References 299

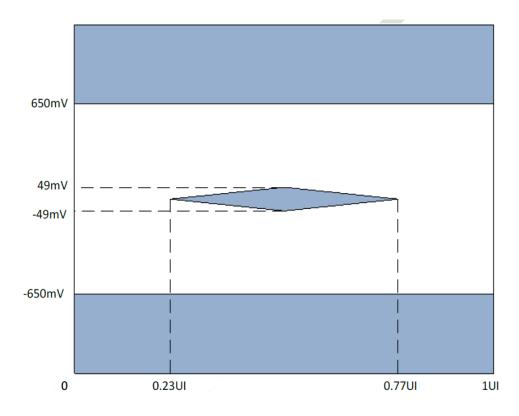

# Tx Eye Diagram TP3 300

Test Overview 300

Test Pass Requirement 300

Test Setup 300

Test Procedure 301

Expected / Observable Results 302

Test References 302

#### Tx Minimum Unit Interval Min/Max 303

Test Overview 303

Test Pass Requirement 303

Test Setup 303

Test Procedure 304

Expected / Observable Results 304

Test References 304

# Tx SSC Down Spread Rate 305

Test Overview 305

Test Pass Requirement 305

Test Setup 305

Test Procedure 306

Expected / Observable Results 306

Test References 306

# Tx SSC Down Spread Range 307

Test Overview 307

Test Pass Requirement 307

Test Setup 307

Test Procedure 308

Expected / Observable Results 308

| Tx SSC Slew Rate 309                                                                                                            |     |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Test Overview 309 Test Pass Requirement 309 Test Setup 309 Test Procedure 310 Expected / Observable Results Test References 310 | 310 |

| Tx SSC Phase Deviation 311                                                                                                      |     |

| Test Overview 311                                                                                                               |     |

| Test Pass Requirement 311                                                                                                       |     |

| Test Setup 311 Test Procedure 312 Expected / Observable Results Test References 312                                             | 312 |

| Tx Eye Diagram 313                                                                                                              |     |

| Test Overview 313 Test Pass Requirement 313 Test Setup 313 Test Procedure 314                                                   |     |

| Expected / Observable Results Test References 315                                                                               | 314 |

| Tx AC Common Mode Voltage                                                                                                       | 316 |

| Test Overview 316 Test Pass Requirement 316 Test Setup 316 Test Procedure 317 Expected / Observable Results Test References 317 | 317 |

| <b>Tx Equalization Tests</b> 318                                                                                                |     |

| Test Overview 318 Test Pass Requirement 318 Test Setup 319 Test Procedure 320 Expected / Observable Results                     | 322 |

| Test References 322                                                                                                             | JZZ |

| Test Pass Requirement 323 Test Setup 323 Test Procedure 324 Measurement Procedure 324 Expected / Observable Results Test References 324 | 324            |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Tx Differential Return Loss Test                                                                                                        | 325            |

| Test Overview 325 Test Pass Requirement 325 Test Setup 326 Test Procedure 329                                                           |                |

| Expected / Observable Results Test References 329                                                                                       | 329            |

| Tx Common Mode Return Loss To                                                                                                           | <b>est</b> 330 |

| Test Overview 330 Test Pass Requirement 330 Test Setup 331 Test Procedure 334                                                           |                |

| Expected / Observable Results Test References 334                                                                                       | 334            |

| Rx Differential Return Loss Test                                                                                                        | 335            |

|                                                                                                                                         |                |

| Test Overview 335 Test Pass Requirement 335 Test Setup 336                                                                              |                |

| Test Pass Requirement 335                                                                                                               | 339            |

| Test Pass Requirement 335 Test Setup 336 Test Procedure 339 Expected / Observable Results                                               |                |

| Test Pass Requirement 335 Test Setup 336 Test Procedure 339 Expected / Observable Results Test References 339                           |                |

Tx Electrical Idle Voltage Test 323

# 8 Transmitter Tests for 20 GB/s Systems

#### Tx Preset Calibration 347 Test Overview 347 Test Setup 347 Test Procedure 349 Expected / Observable Results 349 Test References 349 **SBTX High Voltage** 350 350 Test Overview Test Pass Requirement 350 Test Procedure 350 Expected / Observable Results 351 351 Test References **SBTX Low Voltage** 352 Test Overview 352 Test Pass Requirement 352 352 Test Procedure Expected / Observable Results 353 Test References 353 SBTX Rise/Fall Time Test Overview Test Pass Requirement 354 Test Procedure 355 356 Expected / Observable Results Test References 356 357 SBTX UI Duration 357 Test Overview Test Pass Requirement 357 Test Procedure 358 Expected / Observable Results 359 Test References 359 **SBRX High Voltage Detection** 360 360 Test Overview Test Pass Requirement 360 Test Procedure 361 Expected / Observable Results 361

Test References

361

#### **SBRX Low Voltage Detection** 362 Test Overview 362 362 Test Pass Requirement Test Procedure 362 Expected / Observable Results 362 Test References 362 Tx Rise/Fall Time 363 363 Test Overview Test Pass Requirement 363 Test Setup 363 Test Procedure 364 364 Expected / Observable Results Test References 365 Tx Uncorrelated Jitter Test Overview 365 365 Test Pass Requirement Test Setup 365 Test Procedure 366 Expected / Observable Results 366 Test References 366 Tx Uncorrelated Deterministic Jitter 367 367 Test Overview Test Pass Requirement Test Setup 367 Test Procedure 368 Expected / Observable Results 368 Test References 368 369 Tx Data Dependent Jitter 369 Test Overview Test Pass Requirement 369 Test Setup 369 Test Procedure 370 Expected / Observable Results 370 Test References 370 Tx Duty Cycle Distortion 371 Test Overview 371 Test Pass Requirement Test Setup 371 Test Procedure 372 Expected / Observable Results 372 372 Test References

# Tx Low Frequency Uncorrelated Deterministic Jitter 373

Test Overview 373

Test Pass Requirement 373

Test Setup 373

Test Procedure 374

Expected / Observable Results 374

Test References 374

# **Tx Total Jitter** 375

Test Overview 375

Test Pass Requirement 375

Test Setup 375

Test Procedure 376

Expected / Observable Results 376

Test References 376

#### Tx Uncorrelated Jitter TP3 377

Test Overview 377

Test Pass Requirement 377

Test Setup 377

Test Procedure 378

Expected / Observable Results 378

Test References 378

#### Tx Uncorrelated Deterministic Jitter TP3 379

Test Overview 379

Test Pass Requirement 379

Test Setup 379

Test Procedure 380

Expected / Observable Results 380

Test References 380

# Tx Total Jitter TP3 381

Test Overview 381

Test Pass Requirement 381

Test Setup 381

Test Procedure 382

Expected / Observable Results 383

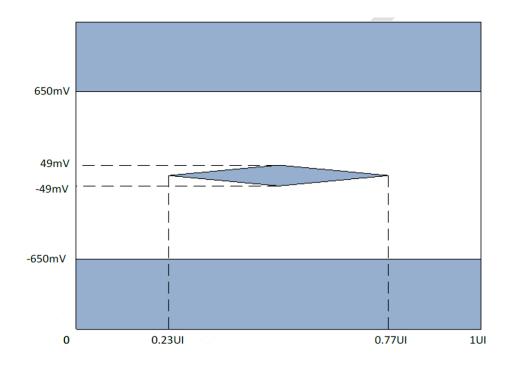

# Tx Eye Diagram TP3 384

Test Overview 384

Test Pass Requirement 384

Test Setup 384

Test Procedure 385

Expected / Observable Results 386

Test References 386

# Tx Minimum Unit Interval, Min/Max 387

Test Overview 387

Test Pass Requirement 387

Test Setup 387

Test Procedure 388

Expected / Observable Results 388

Test References 388

# Tx SSC Down Spread Rate 389

Test Overview 389

Test Pass Requirement 389

Test Setup 389

Test Procedure 390

Expected / Observable Results 390

Test References 390

# Tx SSC Down Spread Range 391

Test Overview 391

Test Pass Requirement 391

Test Setup 391

Test Procedure 392

Expected / Observable Results 392

Test References 392

# Tx SSC Slew Rate 393

Test Overview 393

Test Pass Requirement 393

Test Setup 393

Test Procedure 394

Expected / Observable Results 394

#### Tx SSC Phase Deviation 395 Test Overview 395 395 Test Pass Requirement Test Setup 395 Test Procedure 396 Expected / Observable Results 396 Test References 396 Tx Eye Diagram 397 397 Test Overview Test Pass Requirement 397 Test Setup 397 Test Procedure 398 Expected / Observable Results 398 Test References 399 400 Tx AC Common Mode Voltage Test Overview 400 Test Pass Requirement 400 Test Setup 400 Test Procedure 401 Expected / Observable Results 401 Test References 401 Tx Equalization Tests 402 Test Overview Test Pass Requirement 402 Test Setup 403 Test Procedure 404 Expected / Observable Results 406 406 Test References Tx Electrical Idle Voltage Test 407 Test Overview 407 Test Pass Requirement 407 Test Setup 407 Test Procedure 408 Measurement Procedure 408 Expected / Observable Results 408 Test References 408

# Tx Differential Return Loss Test 409

Test Overview 409

Test Pass Requirement 409

Test Setup 410

Test Procedure 413

Expected / Observable Results 413

Test References 413

# Tx Common Mode Return Loss Test 414

Test Overview 414

Test Pass Requirement 414

Test Setup 415

Test Procedure 418

Expected / Observable Results 418

Test References 418

# Rx Differential Return Loss Test 419

Test Overview 419

Test Pass Requirement 419

Test Setup 420

Test Procedure 423

Expected / Observable Results 423

Test References 423

#### Rx Common Mode Return Loss Test 424

Test Overview 424

Test Pass Requirement 424

Test Setup 425

Test Procedure 428

Expected / Observable Results 428

Test References 428

Index

Contents

# Keysight D9040USBC USB4 Compliance Test Application Methods of Implementation

# 1 Overview

USB4 Automated Testing—At a Glance 30 Required Equipment and Software 31 In This Book 36

# USB4 Automated Testing-At a Glance

The Keysight D9040USBC USB4 Compliance Test Application allows the testing of all the 3<sup>rd</sup> Generation USB devices with the Keysight Infiniium Oscilloscope. These tests are based on the *Universal Serial Bus 4 (USB4®) Specification, Revision 2.0.*

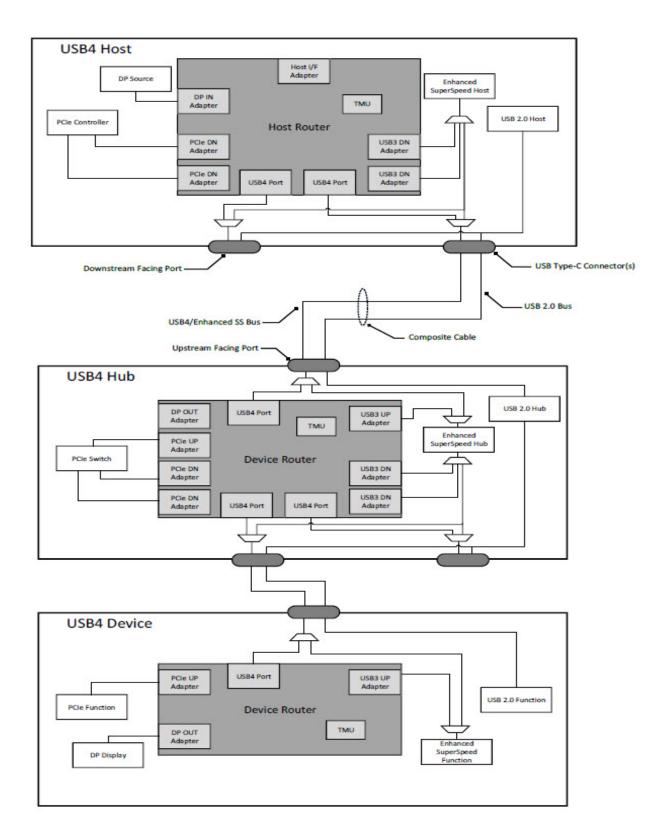

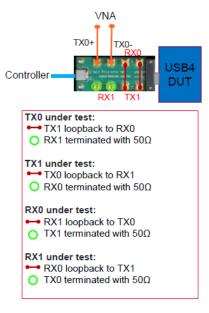

The USB Type-C connector in conjunction with a USB Controller is capable of providing two dual-simplex lanes (or channels). Each lane provides bi-directional 10.3125 GB/s, 20.625 GB/s, 10 GB/s, or 20 GB/s of bandwidth. The USB Type-C connector is capable of connecting USB products when using either a USB Type-C Full Featured cable, a USB Passive cable, a USB Active Electrical or Optical cable, or USB legacy cable or dongle.

#### The USB4 Test Application:

- Lets you select individual or multiple tests to run.

- · Lets you identify the device being tested and its configuration.

- · Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- · Automatically sets up the oscilloscope for each test.

- Provides detailed information for each test that has been run, and lets you specify the thresholds at which marginal or critical warnings appear.

- · Creates a printable HTML report of the tests that have been run.

NOTE

The tests performed by the USB4 Test Application are intended to provide a quick check of the electrical health of the DUT. This testing is not a replacement for an exhaustive test validation plan.

NOTE

Keysight D9040USBC USB4 Compliance Test Application supports; D9010AGGC Compliance Test Software Measurement Server for using multiple machines/PCs over a network as acquisition engines and processing engines in order to significantly enhance the test execution speed. To know more, please see the D9010AGGC product page on keysight.com.

# Required Equipment and Software

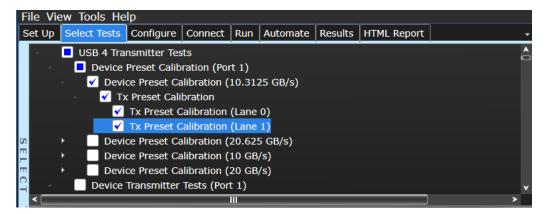

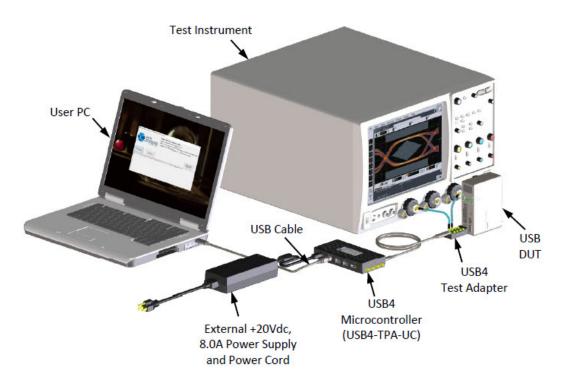

In order to run the USB4 automated tests, you need the following equipment and software:

# Hardware

- Use one of the Oscilloscope models given in Table 1.

- Keyboard, qty = 1, (provided with the Keysight Infiniium oscilloscope)

- Mouse, qty = 1, (provided with the Keysight Infiniium oscilloscope)

- · Keysight also recommends using a second monitor to view the test application.

Table 1 lists the recommended test equipments for running the USB4 tests. Note that all test equipments require Calibration to ensure accurate and repeatable results. The test equipments must be calibrated prior to, and if necessary, during the test procedure.

Table 1 Test Equipments and Accessories for USB4 Tests

| Required Equipment       | Test Equipment Capabilities/Description                                                             | Recommended Test Equipment                                                                                                                                                                                                                                                                                |

|--------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Point Access Boards | TPA Boards provide test point for the pins on the USB connector and an easy way to control the DUT. | <ul> <li>USB Plug Test Fixture or equivalent</li> <li>Wilder TBT-TPA-UHG2         TBT/USB4 Micro-Controller Test             Module with USB Cable or equivalent     </li> <li>Wilder USB4-TPA-UC         USB4 Micro-Controller Test Module             with USB Cable (Type A to Type B)     </li> </ul> |

| Required Equipment                                                                                                                                                              | Test Equipment Capabilities/Description                                                                                                                                                                                                                                                                                 | Recommended Test Equipment                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                 | DC to 21±1GHz -3dB bandwidth or greater  80G sample/sec Sampling rate or greater, sampling 2 channels simultaneously  Sample memory: 2 channels at 50M samples per channel or greater  1st and 2nd order CDR capability  Equalization for USB 3.1 model capability                                                      | Keysight Z-Series Oscilloscope (25GHz and above)                                                                                                                                         |

| Real Time Scopes (choose from one of the available                                                                                                                              | <ul> <li>DC to 21±1GHz -3dB bandwidth or greater</li> <li>128G sample/sec Sampling rate or greater, sampling 2 channels simultaneously</li> <li>Sample memory: 2 channels at 50M samples per channel or greater</li> <li>1st and 2nd order CDR capability</li> <li>Equalization for USB 3.1 model capability</li> </ul> | Keysight UXR Series Oscilloscope<br>(25GHz and above)                                                                                                                                    |

| <ul> <li>80G sar samplin</li> <li>Sample channe</li> <li>1st and</li> <li>Equalize</li> <li>DC to 2</li> <li>80G sar samplin</li> <li>Sample channe</li> <li>1st and</li> </ul> |                                                                                                                                                                                                                                                                                                                         | Keysight V-Series Oscilloscope (25GHz and above)                                                                                                                                         |

|                                                                                                                                                                                 | <ul> <li>DC to 21±1GHz -3dB bandwidth or greater</li> <li>80G sample/sec Sampling rate or greater, sampling 2 channels simultaneously</li> <li>Sample memory: 2 channels at 50M samples per channel or greater</li> <li>1st and 2nd order CDR capability</li> <li>Equalization for USB 3.1 model capability</li> </ul>  | Keysight Q-Series Oscilloscope (25GHz and above)                                                                                                                                         |

| Accessories                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                          |

| Low insertion loss phase matched cables                                                                                                                                         | <ul> <li>Phase matched ±2° @ 40GHz</li> <li>Max IL in 10GHz &lt; 1.2dB</li> </ul>                                                                                                                                                                                                                                       | <ul> <li>Rosenberger UK Micro Coax         FC142A0-014-MTIE 2.92m (x2) L-1m         (40GHz)</li> <li>Rosenberger Adaptor: RPC-2.92 female         – SMP female – 02K119-K00E3</li> </ul> |

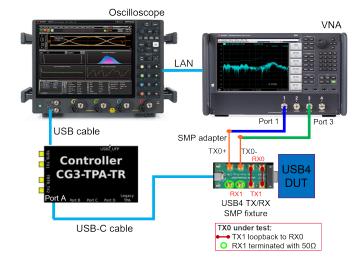

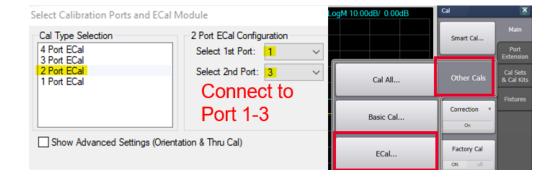

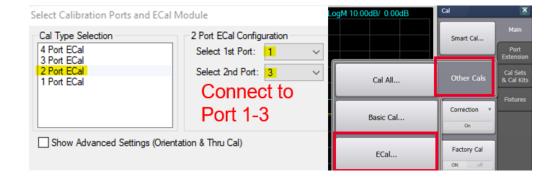

# VNA Configuration Requirements

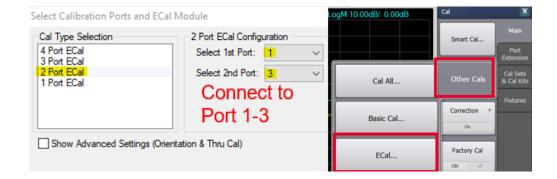

| Required Equipment | Equipment Description                                                                                                                                                                                                                                                                                            | Qty    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

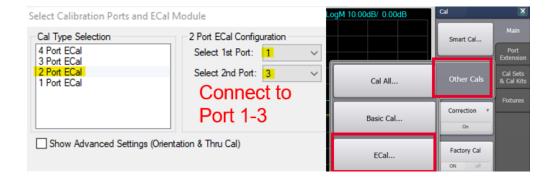

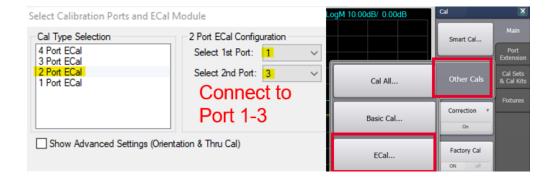

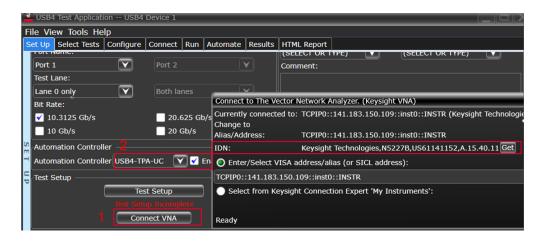

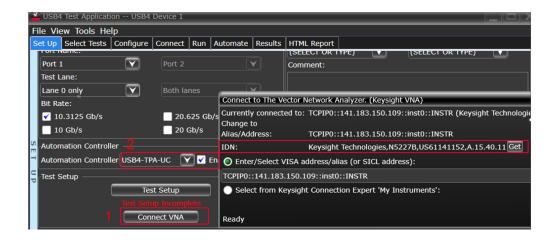

| Network Analyzer   | Keysight Vector Network Analyzer:  20 GHz is recommended as USB4 requires measurements up to 20 GHz.  Minimum 4-Port VNA to support USB4 SigTest tool requirement.  E5080B-4K0: 4-port test set, 9 kHz to 20 GHz or  P5024A-400 Streamline USB Series VNA or  M9804A-400 PXI Multiport VNA or  N522xB 4-Port PNA | 1 each |

|                    | Note 1:<br>Ensure that the VNA firmware revision is A.17.25.05 or higher to be compatible with the return loss test automation.<br>(Windows 10)                                                                                                                                                                  |        |

|                    | Note 2:<br>All 2-Port VNA and legacy E5071C will not be supported. Please refer to Return<br>Loss Test MOI for manual setup.                                                                                                                                                                                     |        |

| ECal Module        | 4-Port Electronic Calibration (ECal) Module • N4433D-010/ODC 4-Ports                                                                                                                                                                                                                                             | 1 each |

#### Software

- The minimum version of Infiniium oscilloscope software (see the Keysight D9040USBC USB4 Compliance Test Application Release Notes)

- Keysight D9040USBC USB4 Compliance Test Application software

- SigTest setup software list:

- · Matlab runtime compiler MCR R2021b (9.11)

- USB4 SigTest tool

- · USB4 ETT tool

- · Wilder USB4 microcontroller USB drivers

- · Wilder USB4 microcontroller UI executable

- · FTDI chip driver

For more information on SigTest setup, please see **Keysight D9040USBC USB4 Compliance Test Application Online Help > Setting Up the Test Environment > SigTest Setup.**

# Licensing information

Refer to the *Data Sheet* pertaining to USB4 Test Application to know about the licenses you must install along with other optional licenses. Visit "http://www.keysight.com/find/D9040USBC" and in the web page's **Resources** tab, you may view the associated Data Sheet.

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

The licensing format for Keysight License Manager 6 differs from its predecessors. See "Installing the License Key" on page 39 to see the difference in installing a license key using either of the applications on your machine.

# In This Book

This manual describes the tests that are performed by the USB4 Test Application in more detail.

- Chapter 2, "Installing the Test Application and Licenses" describes how to install the software and licenses for the USB4 Test Application software (if it was purchased separately).

- Chapter 3, "Preparing to Take Measurements" describes how to start the USB4 Test Application and gives a brief overview of its features.

- Chapter 4, "Host / Device USB4 Transmitter Testing" contains an overview on the USB system components and requirements for Transmitter testing.

- Chapter 5, "Transmitter Tests for 10.3125 GB/s Systems" describes procedures to run electrical tests on a USB DUT operating at a bit rate of 10.3125 GB/s.

- Chapter 6, "Transmitter Tests for 10 GB/s Systems" describes procedures to run electrical tests on a USB DUT operating at a rounded-off bit rate of 10 GB/s.

- Chapter 7, "Transmitter Tests for 20.625 GB/s Systems" describes procedures to run electrical tests on a USB DUT operating at a bit rate of 20.625 GB/s.

- Chapter 8, "Transmitter Tests for 20 GB/s Systems" describes procedures to run electrical tests on a USB DUT operating at a rounded-off bit rate of 20 GB/s.

#### See Also

The Keysight D9040USBC USB4 Compliance Test Application's Online Help, which describes:

- · Starting the USB4 Test Application

- · Creating or Opening a Test Project

- · Setting Up the Test Environment

- Selecting Tests

- Configuring Tests

- · Verifying Physical Connections

- Running Tests

- Configuring Automation in the Test Application

- · Viewing Results

- · Viewing HTML Test Report

- · Exiting the Test Application

- · Additional Settings in the Test App

# References

The USB standard specifications are available in Universal Serial Bus 4 (USB4™) Specification Version 1.0.

# 2 Installing the Test Application and Licenses

Installing the Test Application / 38 Installing the License Key / 39

If you purchased the Keysight D9040USBC USB4 Compliance Test Application separate from your Infiniium oscilloscope, you must install the software and license key.

For information on SigTest setup, please see **Keysight D9040USBC USB4 Compliance Test Application Online Help > Setting Up the Test Environment > SigTest Setup.**

#### 2

# Installing the Test Application

- 1 Make sure you have the minimum version of Infiniium Oscilloscope software (see the D9040USBC USB4 Test Application release notes). To ensure that you have the minimum version, select **Help > About Infiniium...** from the main menu.

- 2 To obtain the USB4 Test Application, go to Keysight website: "http://www.keysight.com/find/D9040USBC".

- 3 In the web page's **Trials & Licenses** tab, click the **Details and Download** button to view instructions for downloading and installing the application software.

# Installing the License Key

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

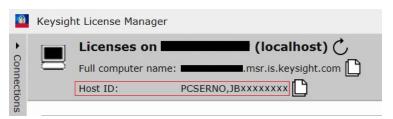

Using Keysight License Manager 5

To view and copy the Host ID from Keysight License Manager 5:

- 1 Launch Keysight License Manager on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID that appears on the top pane of the application. Note that x indicates numeric values.

Figure 1 Viewing the Host ID information in Keysight License Manager 5

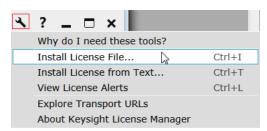

To install one of the procured licenses using Keysight License Manager 5 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager.

- 3 From the configuration menu, use one of the options to install each license file.

Figure 2 Configuration menu options to install licenses on Keysight License Manager 5

For more information regarding installation of procured licenses on Keysight License Manager 5, refer to Keysight License Manager 5 Supporting Documentation.

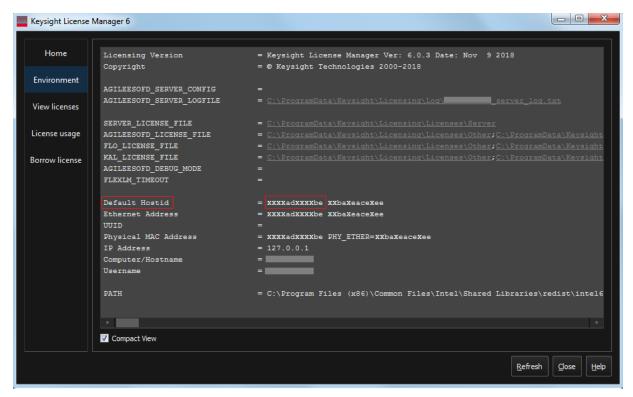

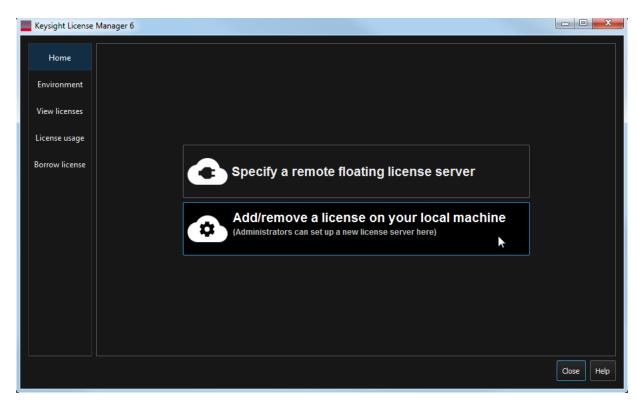

#### Using Keysight License Manager 6

To view and copy the Host ID from Keysight License Manager 6:

- 1 Launch Keysight License Manager 6 on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID, which is the first set of alphanumeric value (as highlighted in Figure 3) that appears in the Environment tab of the application. Note that x indicates numeric values.

Figure 3 Viewing the Host ID information in Keysight License Manager 6

To install one of the procured licenses using Keysight License Manager 6 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager 6.

- 3 From the Home tab, use one of the options to install each license file.

Figure 4 Home menu options to install licenses on Keysight License Manager 6

For more information regarding installation of procured licenses on Keysight License Manager 6, refer to Keysight License Manager 6 Supporting Documentation.

2 Installing the Test Application and Licenses

Keysight D9040USBC USB4 Compliance Test Application Methods of Implementation

# 3 Preparing to Take Measurements

Calibrating the Oscilloscope / 44

Starting the USB4 Test Application / 45

Setting up the USB4 Test Application / 48

Calibration Setup for Compliance Tests / 56

Before running the automated tests, you should calibrate the oscilloscope. After the oscilloscope has been calibrated, you are ready to start the USB4 Test Application and perform the measurements.

For information on SigTest setup, please see **Keysight D9040USBC USB4 Compliance Test Application Online Help > Setting Up the Test Environment > SigTest Setup.**

# Calibrating the Oscilloscope

If you have not already calibrated the oscilloscope, refer to the *User Guide* for the respective Oscilloscope you are using.

NOTE

If the ambient temperature changes more than 5 degrees Celsius from the Calibration temperature, internal Calibration should be performed again. The delta between the Calibration temperature and the present operating temperature is shown in the **Utilities > Calibration** menu.

NOTE

If you switch cables between channels or other Oscilloscopes, it is necessary to perform cable and probe Calibration again. Keysight recommends that, once Calibration is performed, you label the cables with the channel on which they were calibrated.

### Starting the USB4 Test Application

1 Ensure that the USB4 Device Under Test (DUT) is operating and set to desired test modes. To start the USB4 Test Application: From the Infiniium Oscilloscope's main menu, select Analyze > Automated Test Apps > D9040USBC USB4 Test App

NOTE

The **Test Lane** drop-down options in the **Set Up** tab, when the Test App is launched on a 4-Channel Oscilloscope, are different from that on a 2-Channel Oscilloscope.

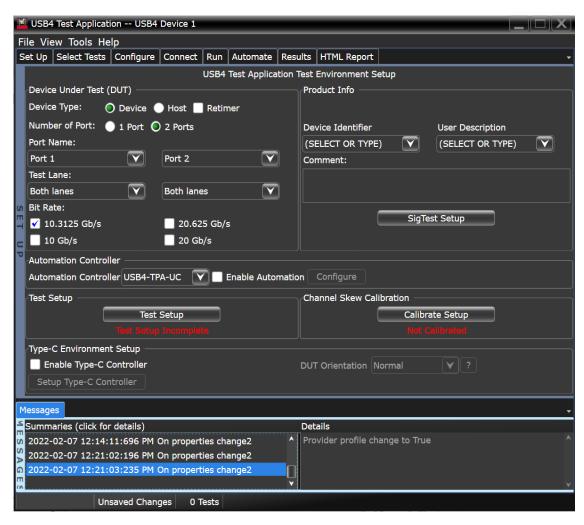

Figure 5 USB4 Test Application default window on 4-Ch Oscilloscope

Figure 6 USB4 Test Application default window on 2-Ch Oscilloscope

To understand the functionality of the various features in the user interface of the Test Application, refer to the *Keysight D9040USBC USB4 Compliance Test Application Online Help* available in the Help menu.

The task flow pane and the tabs in the main pane show the steps you take in running the automated tests:

| Set Up       | Lets you identify and set up the test environment, including information about the device under test. The Test App includes relevant information in the final HTML report.                                                                                                 |  |

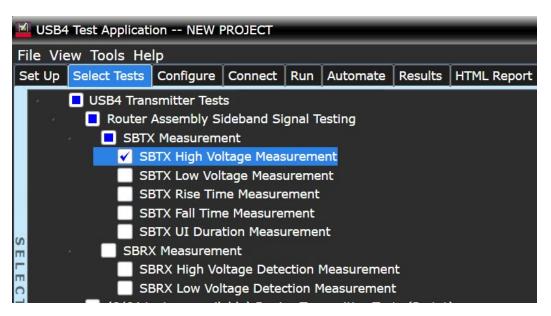

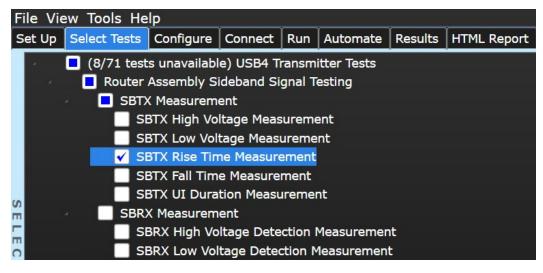

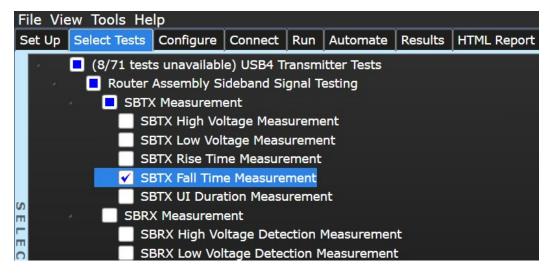

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically so you can select all tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.      |  |

| Configure    | Lets you configure test parameters (for example, channels used in test, voltage levels, etc.).                                                                                                                                                                             |  |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests that are to be run.                                                                                                                                                                       |  |

| Run          | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |  |

| Automate     | Lets you construct scripts of commands that drive execution of the application.                                                                                                                                                                                            |  |

| Results      | Contains more detailed information about the tests that have been run. You can change the thresholds at which marginal or critical warnings appear.                                                                                                                        |  |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |  |

# NOTE

In the **Configure** tab, the values for all such configuration parameters that are oscilloscope-dependent, will correspond to the oscilloscope model (DSOs or UXRs), where you are running the Test Application.

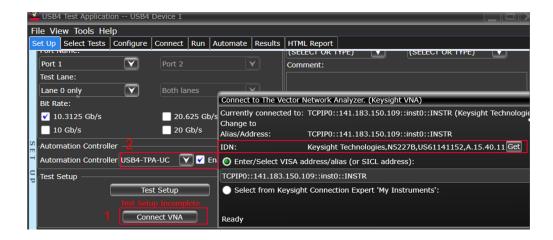

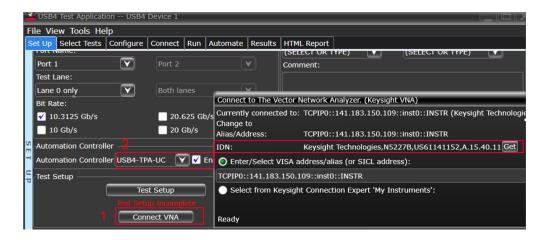

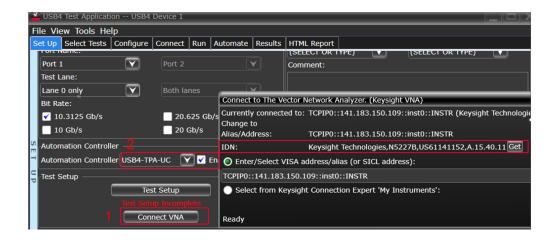

# Setting up the USB4 Test Application

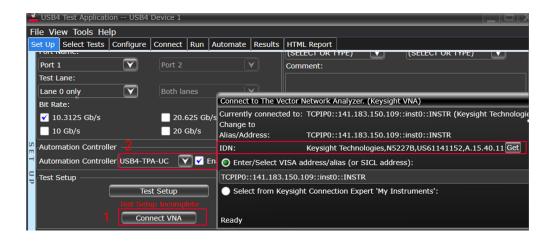

In order to run the electrical compliance tests on a USB DUT operating at a bit rate of either 10.3125 GB/s, 20.625 GB/s, 10 GB/s. 20 GB/s or all, you must set up the USB4 Test Application to be able to view and select the required tests.

- 1 Start the USB4 Test Application. See "Starting the USB4 Test Application" on page 45.

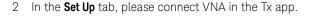

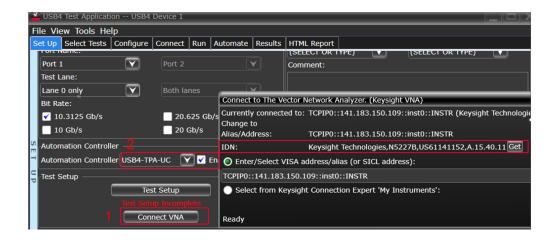

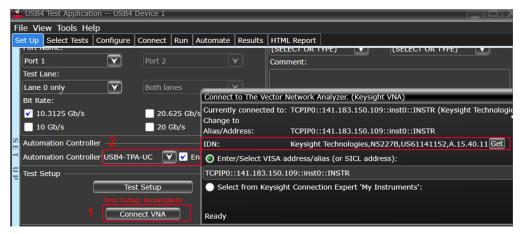

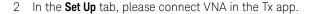

- 2 Under the **Set Up** tab, select the following options, as shown in Figure 7.

- a Device Type: Select DUT Type as either Device (default) or Host.

- b Number of Port: Select 1 Port (default) or 2 Ports.

- c **Port Name:** —This drop-down field allows you to select a port name or even type a custom name for the ports being used for testing. Default values are **Port 1** and **Port 2**.

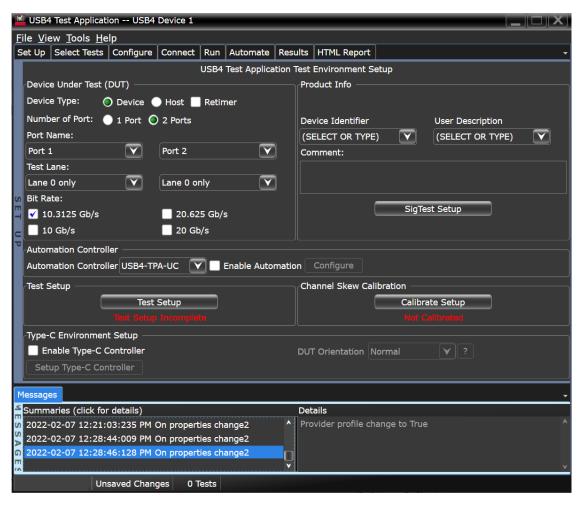

- d **Test Lane:** The drop-down options, when the Test App is launched on a 4-Channel Oscilloscope, are different from that on a 2-Channel Oscilloscope.

- On a 4-Channel Oscilloscope—From the drop-down options, select either Both Lanes (default), Lane 0 only or Lane 1 only; depending on the number of lanes being used for testing.

- On a 2-Channel Oscilloscope—From the drop-down options, select either Lane 0 only or Lane 1 only; depending on the number of lanes being used for testing.

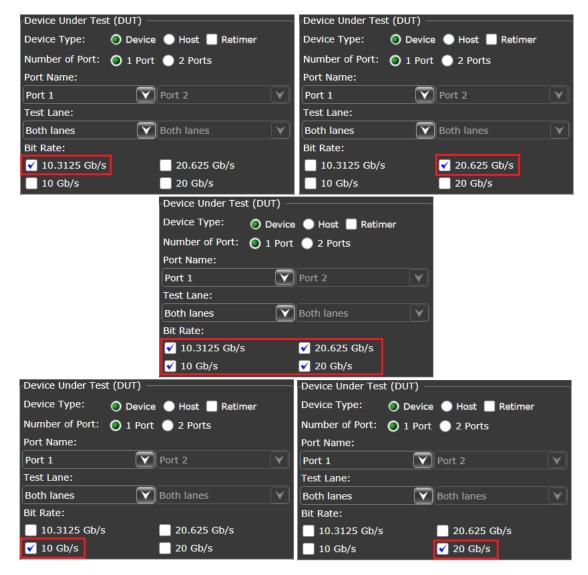

- e Bit Rate Select either one or more bit-rates to indicate the signal speed on the DUT.

- f **Product Info** Helps you in proper identification of the DUT on HTML reports. This option is particularly useful when running compliance tests on multiple DUTs.

- **Device Identifier:** Type an appropriate name/identifier for the DUT, which is being tested. The entries are saved such that you may select the values again later, if required.

- **User Description:** Type an appropriate description for the DUT, which is being tested. The entries are saved such that you may select the values again later, if required.

- **Comment:** Type appropriate comments, if required.

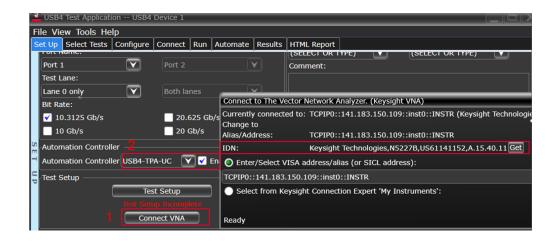

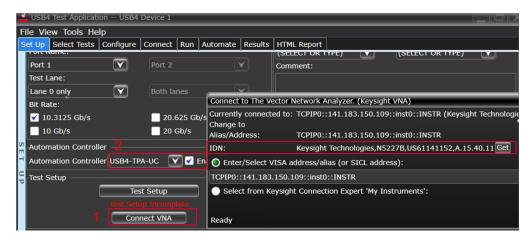

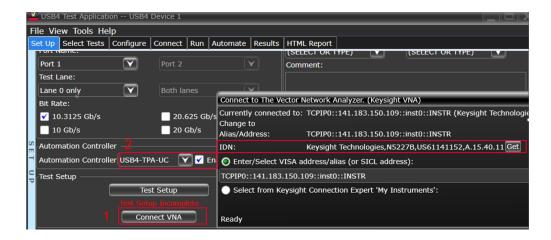

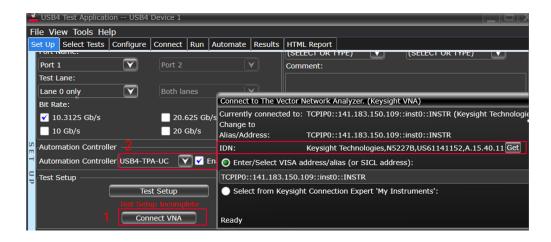

- g USB Automation Controller Select Enable Automation check box, then select the required Automation Controller from the drop down box. Supported automation controllers are: USB4-TPA-UC (Wilder USB4 microcontroller), TBT-TPA-UHG2 (Wilder Thunderbolt microcontroller), and TCPIP.

- h USB Type-C Test Controller Select Enable Type-C Controller check box, then click the Setup Type-C Controller button to configure the N7018A Type C Test Controller. Please note, N7018A can only be used with the Wilder Thunderbolt microcontroller.

#### NOTE

- When testing USB4: Please use the "Wilder USB4 controller + Wilder fixture".

- When testing TBT3: Please use either the "Wilder TBT3 controller + Wilder fixtures" or "the Wilder TBT3 controller + N7018A + N7015A".

For more information about using the **USB Automation Controller** and **USB Type-C Test Controller** features, refer to the *Keysight D9040USBC USB4 Compliance Test Application Online Help.*

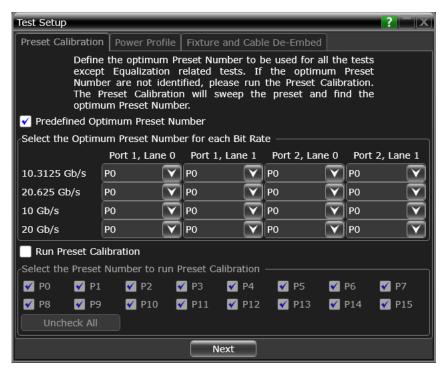

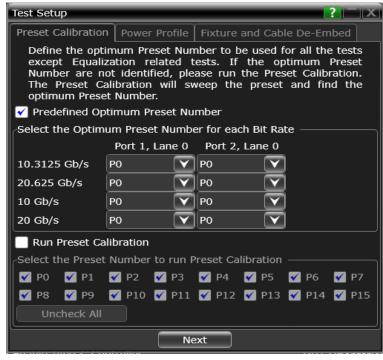

- *i* **Test Setup** Click the **Test Setup** button to set up the following Calibration prerequisites:

- Preset Calibration Required to run the Transmitter Preset Calibration tests.

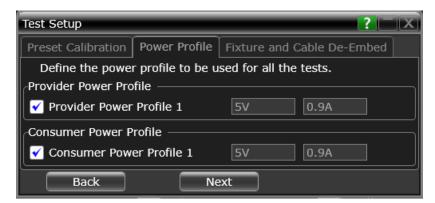

- Power Profile Appears only when the Enable Type-C Controller is selected. Defines the

power supply and demand requirements of a USB DUT with Type-C implementation,

which may be connected either as a provider or a consumer.

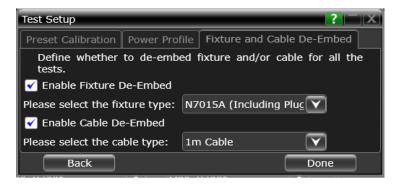

- Fixture and Cable De-Embed Define whether to de-embed a fixture or a cable for all the tests.

- j Channel Skew Calibration Click the Calibrate Setup button to perform Channel Skew Calibration before running the tests. Please perform channel skew calibration on the exact oscilloscope channels where the DUT is connected.

See "Calibration Setup for Compliance Tests" on page 56 for more information on these Calibration options.

Figure 7 Set Up options for DUT Type "Device" on a 4-Channel Oscilloscope

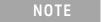

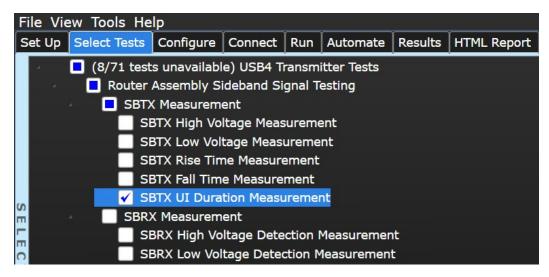

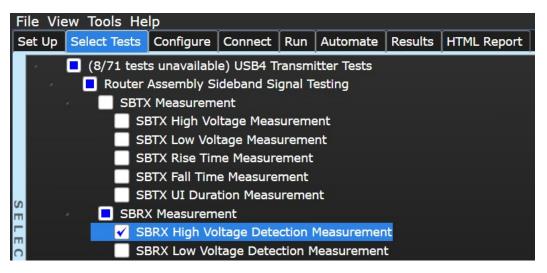

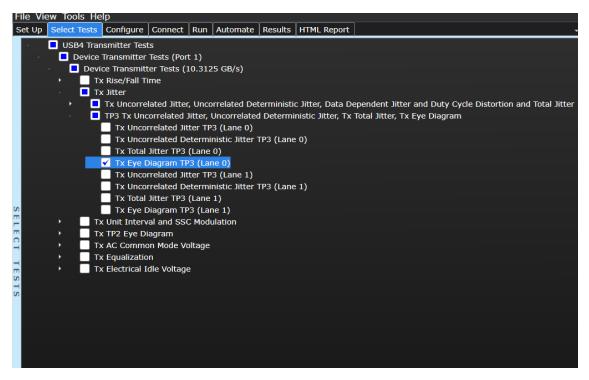

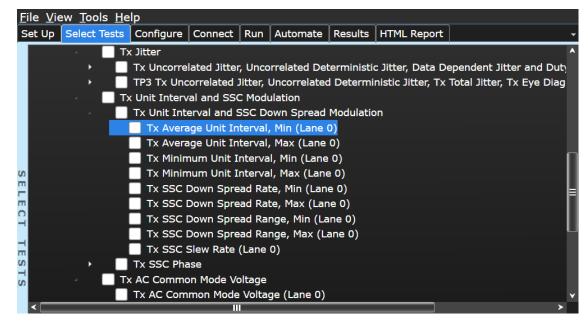

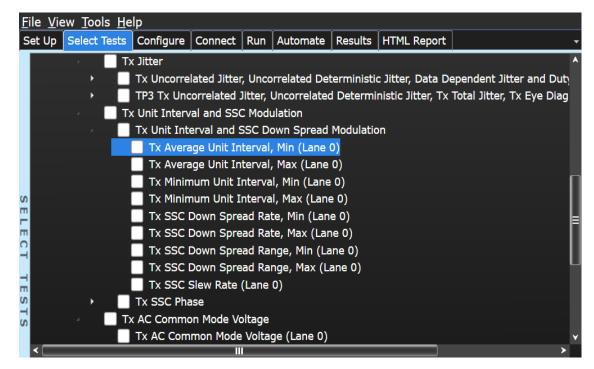

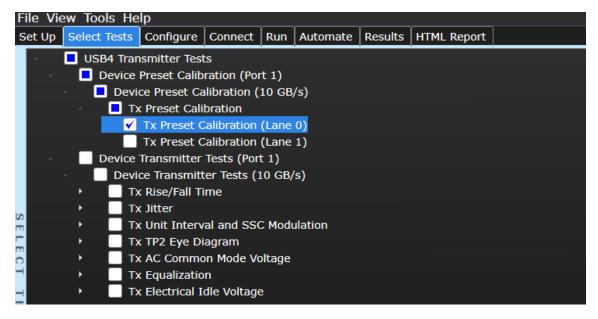

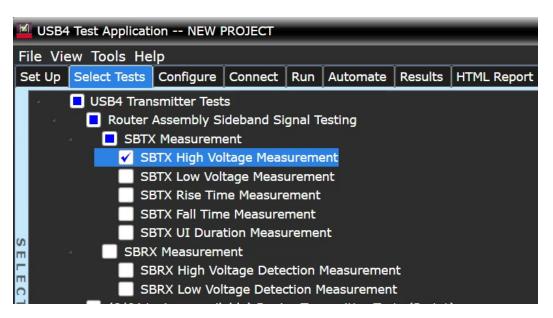

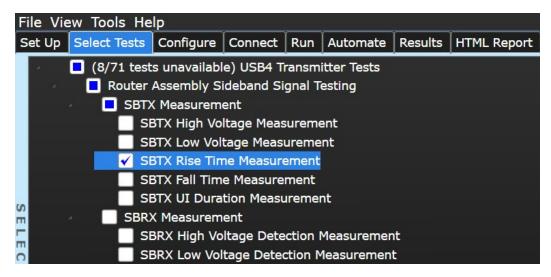

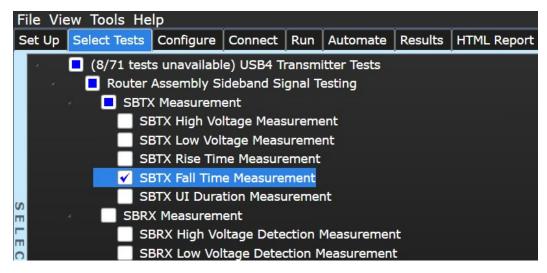

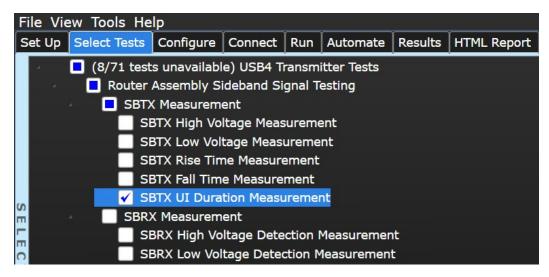

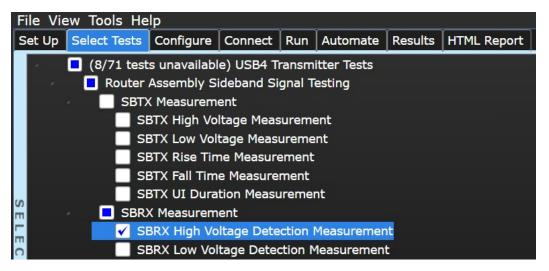

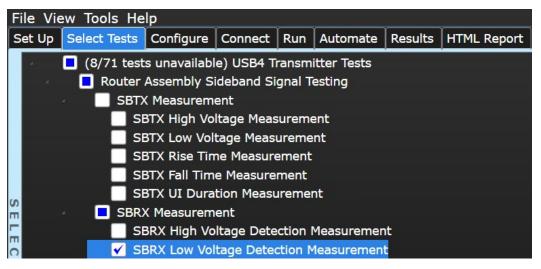

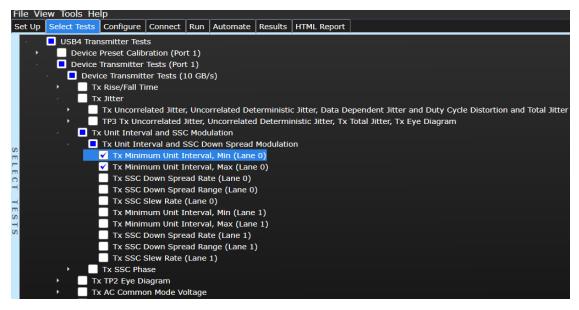

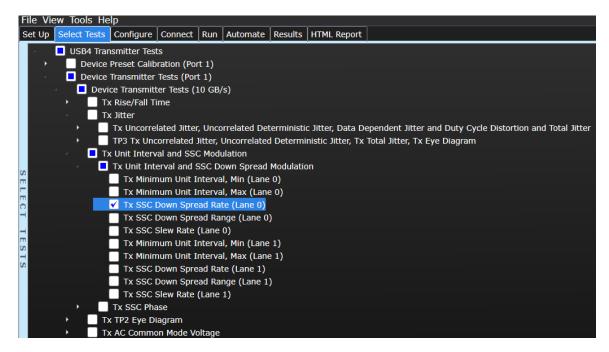

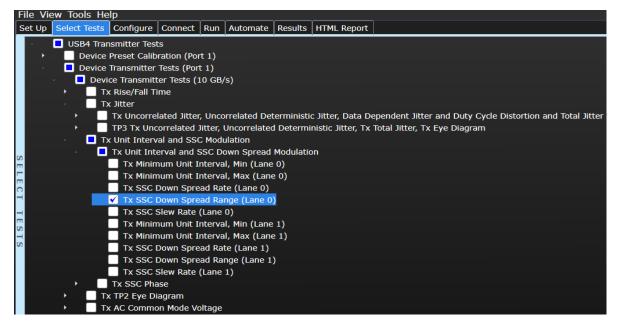

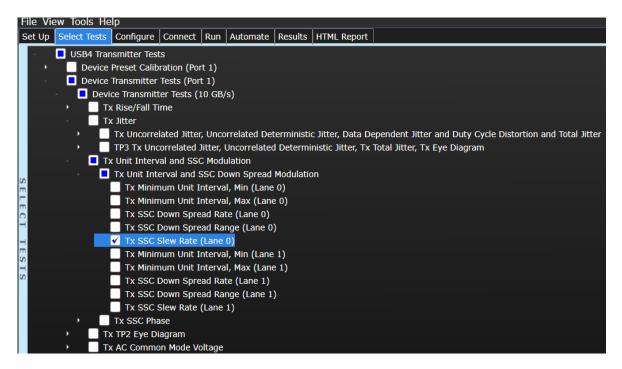

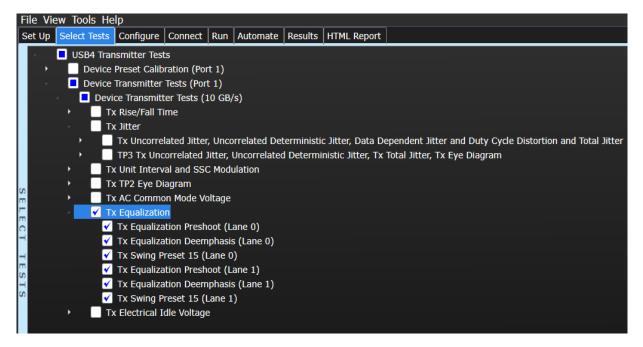

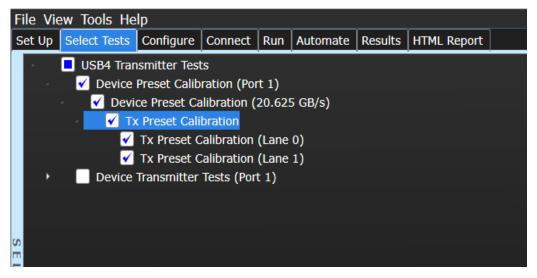

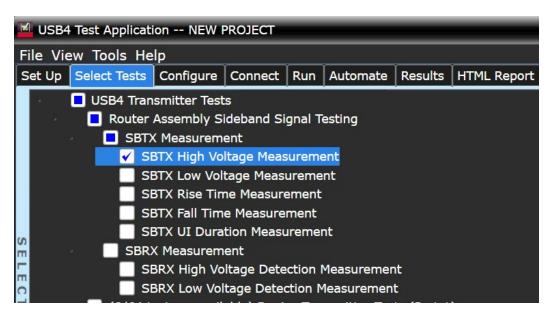

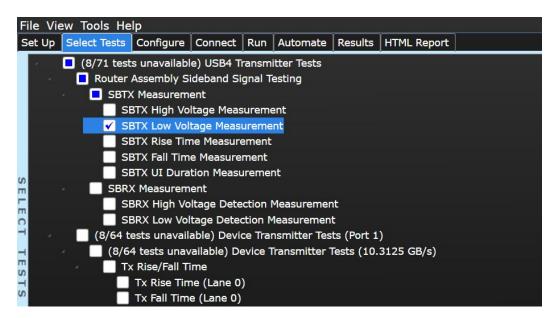

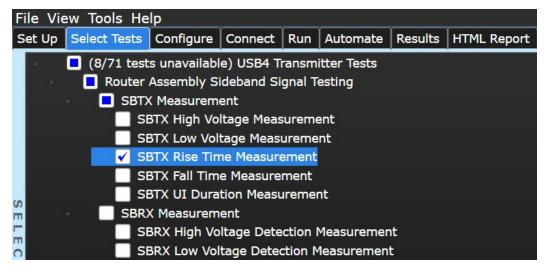

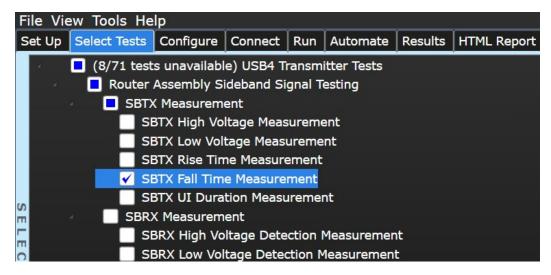

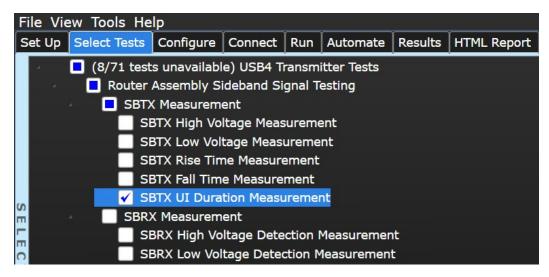

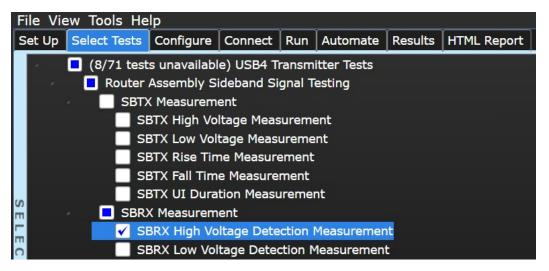

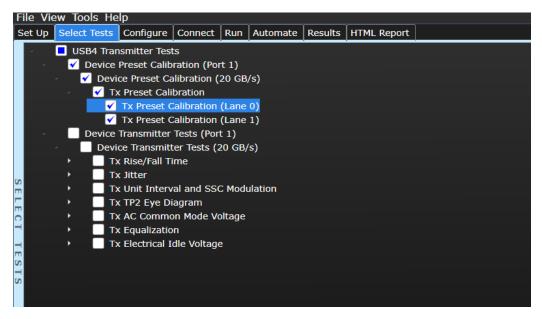

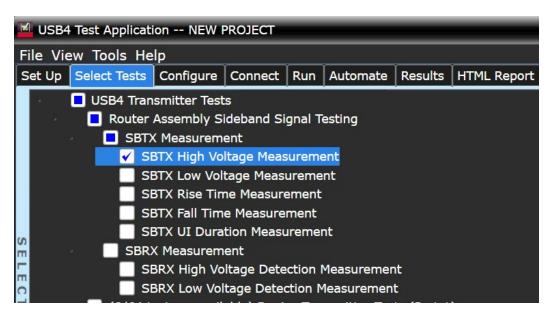

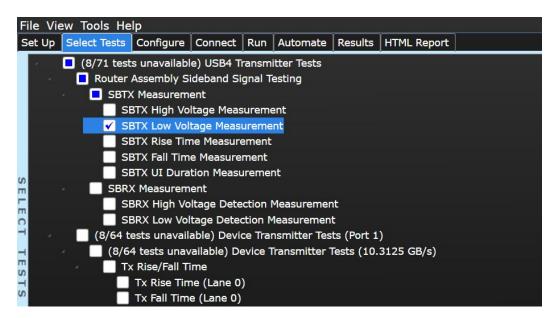

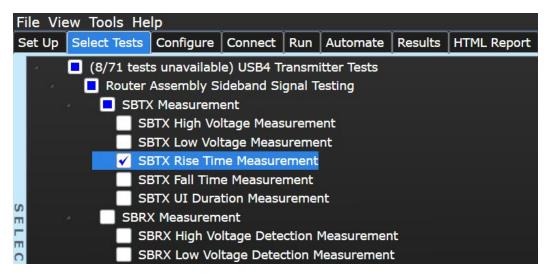

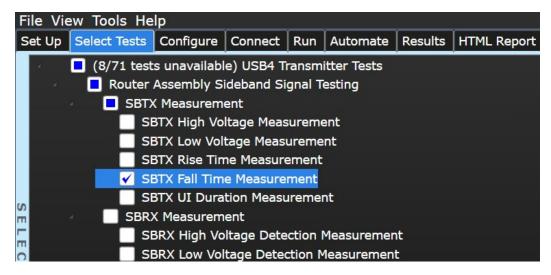

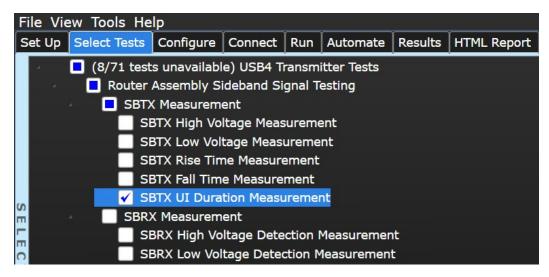

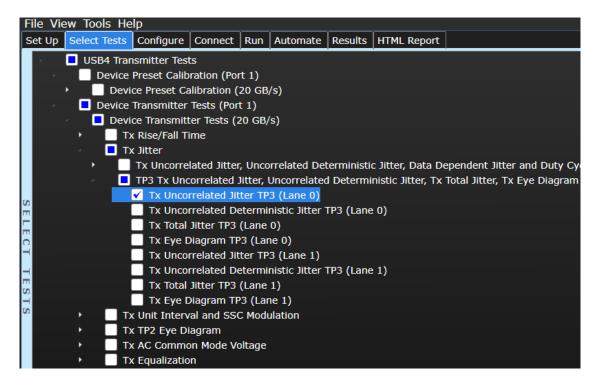

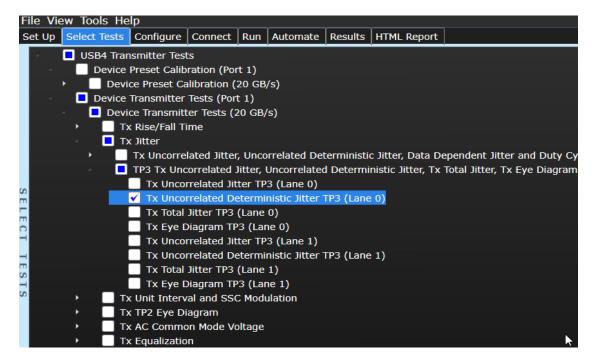

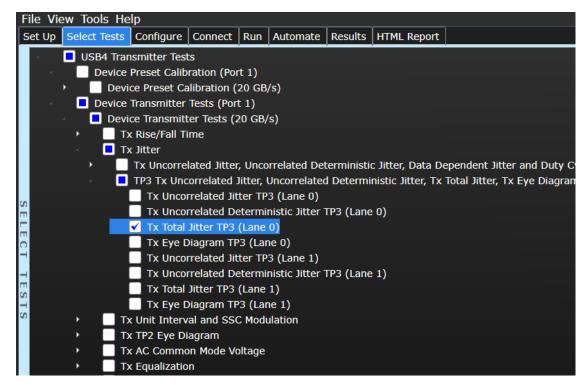

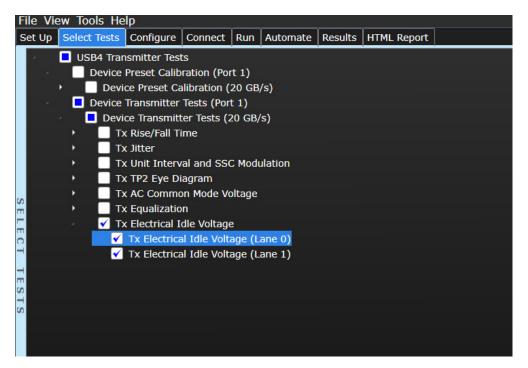

3 Based on your choices under the **Set Up** tab, the **Select Tests** tab filters tests into test groups corresponding to one or more selected bit-rates and the selected option for device type, port and lane.

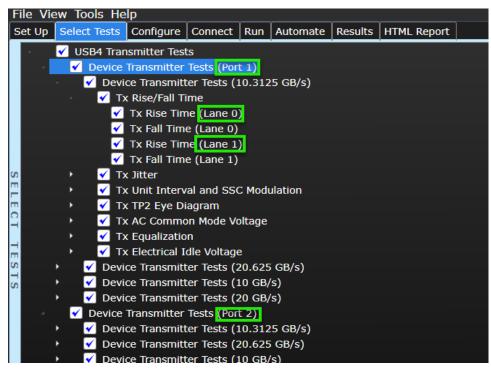

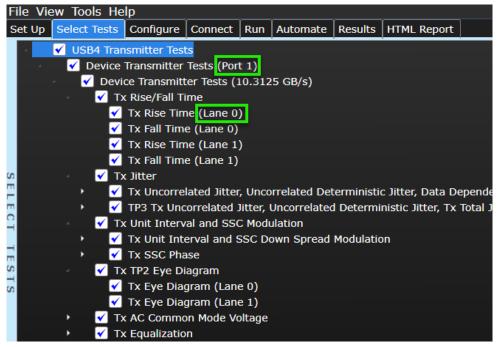

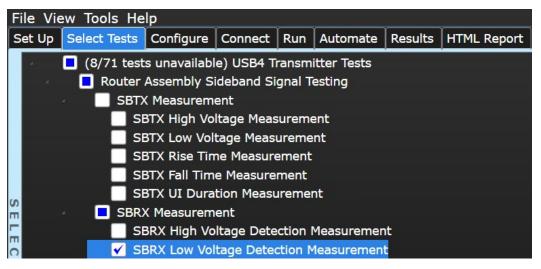

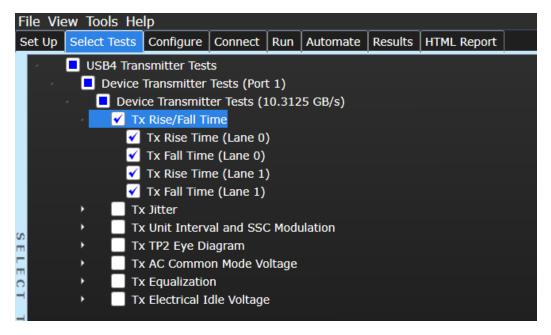

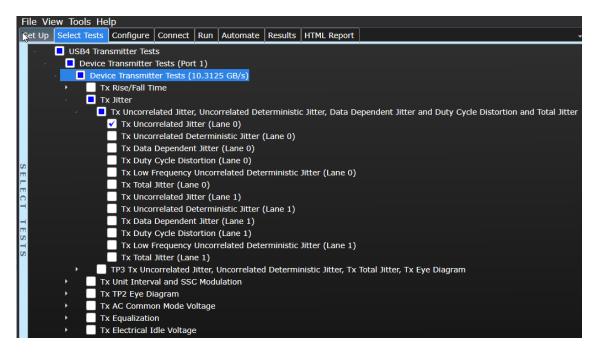

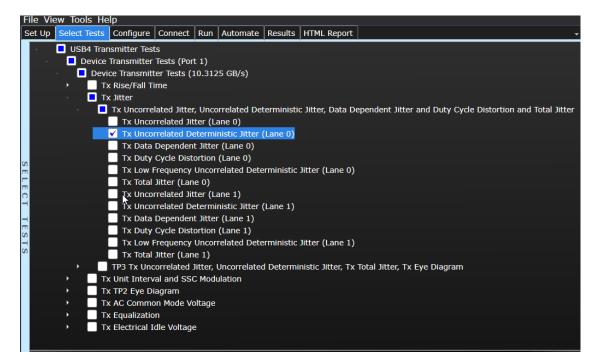

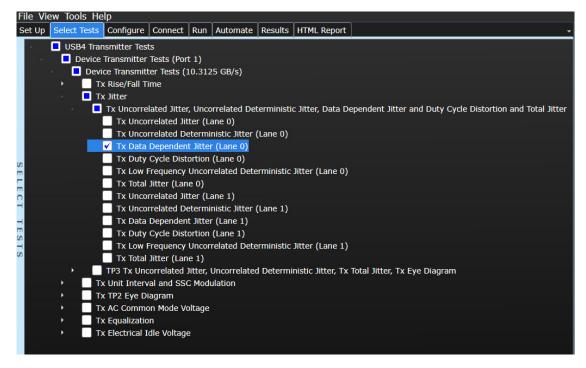

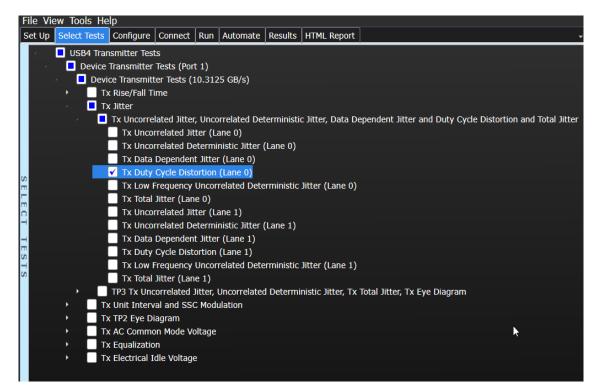

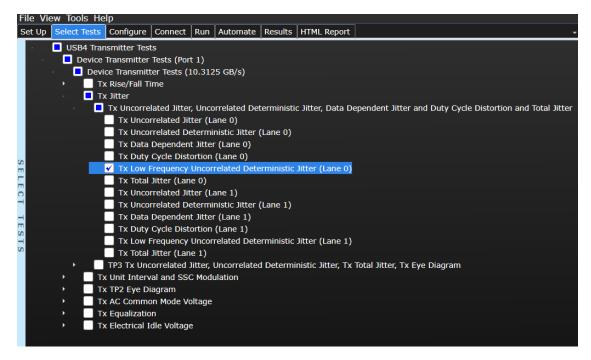

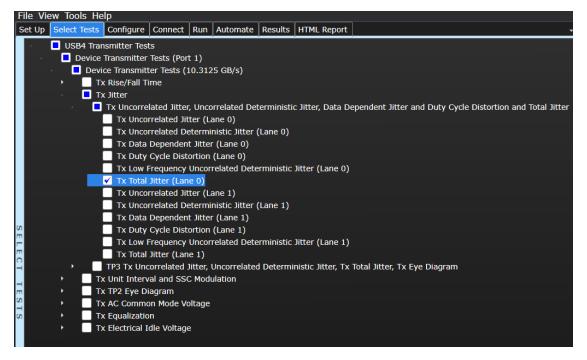

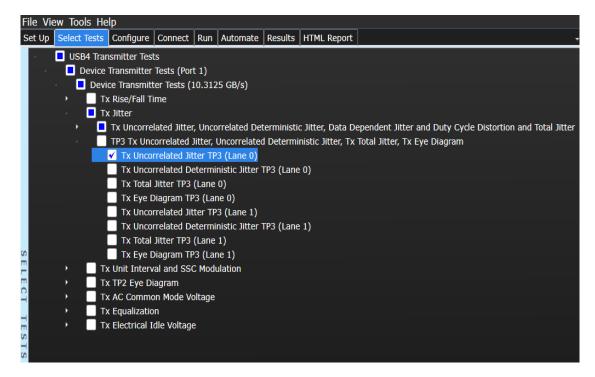

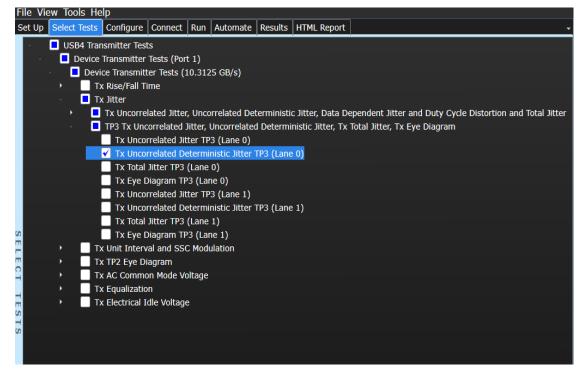

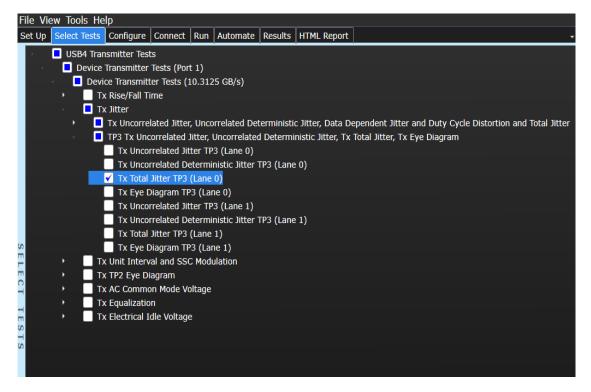

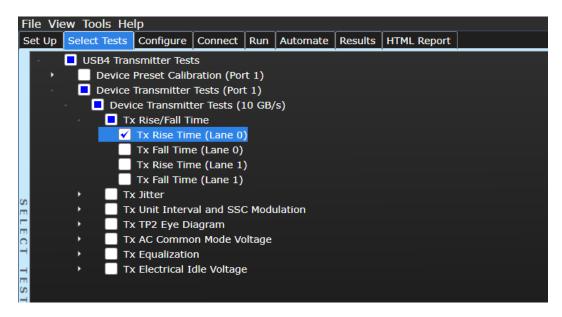

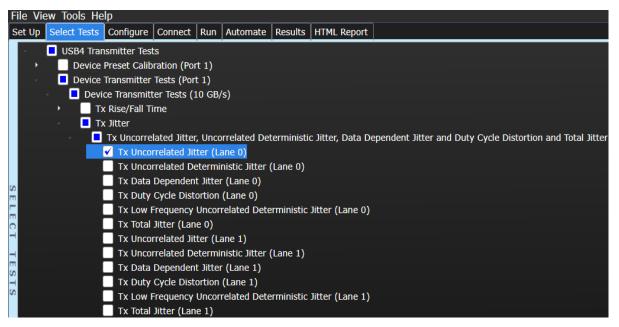

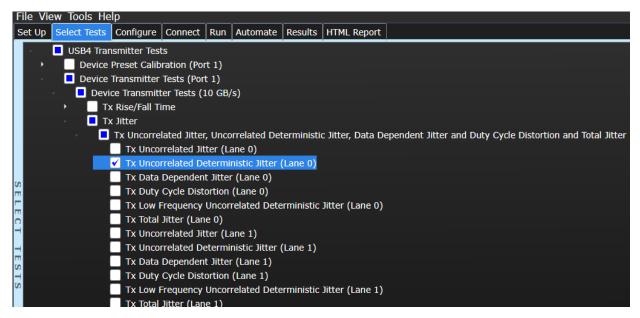

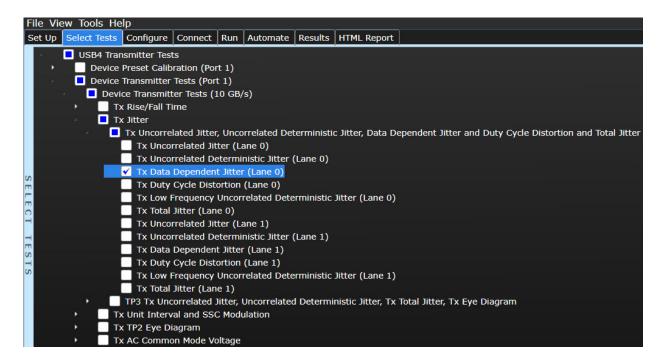

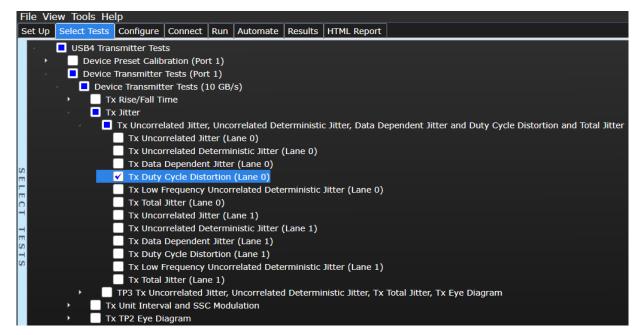

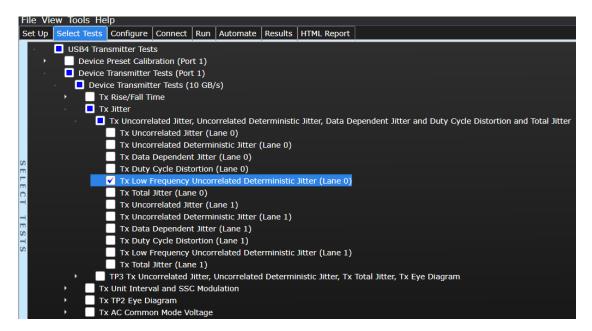

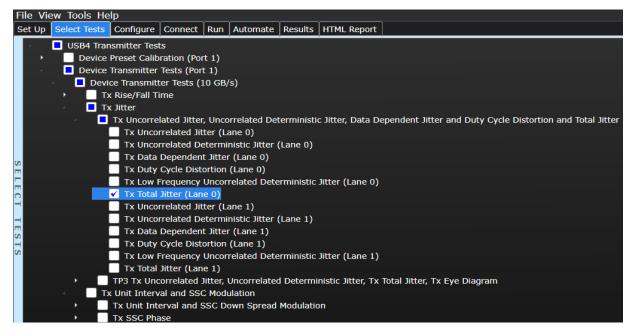

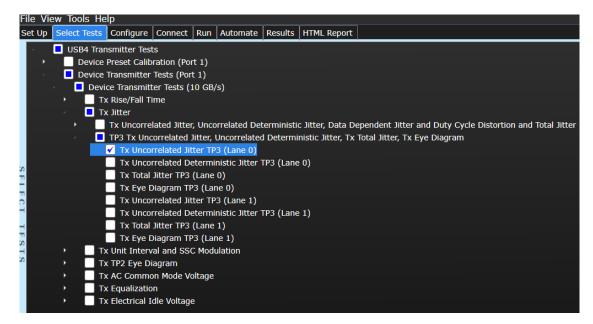

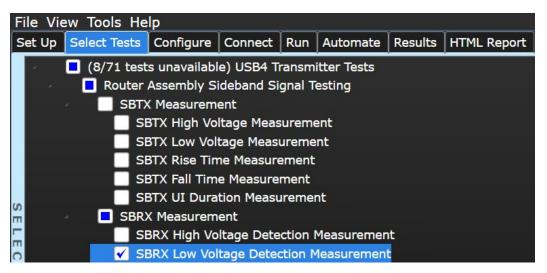

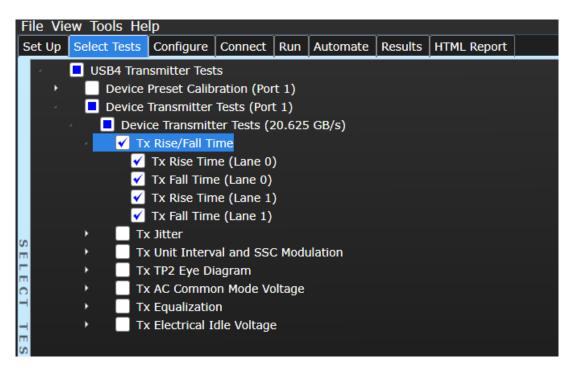

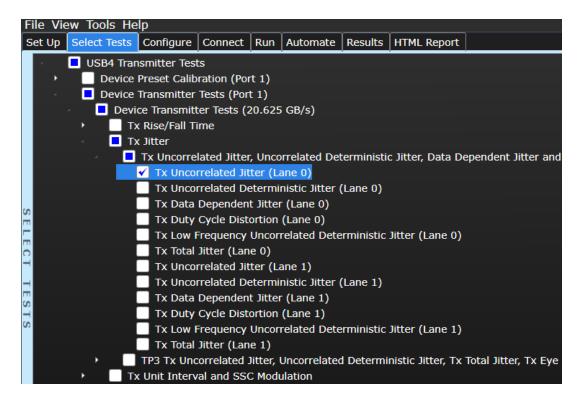

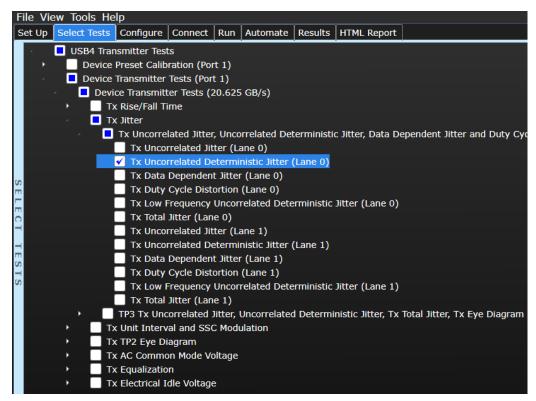

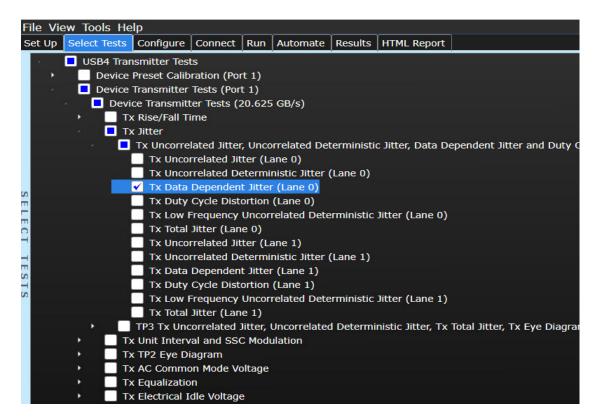

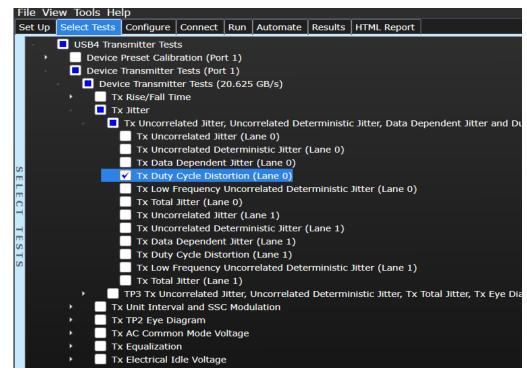

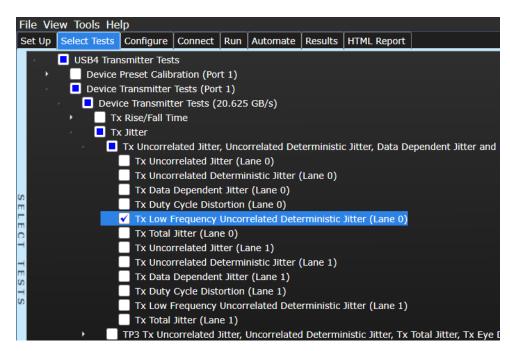

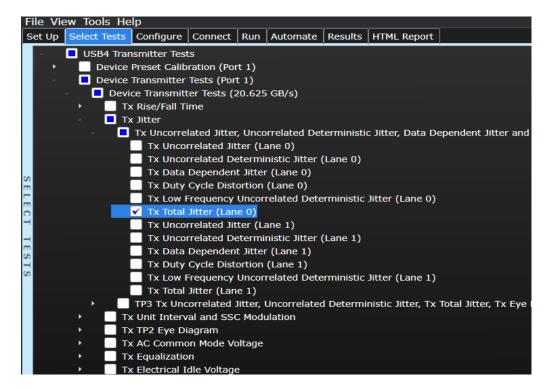

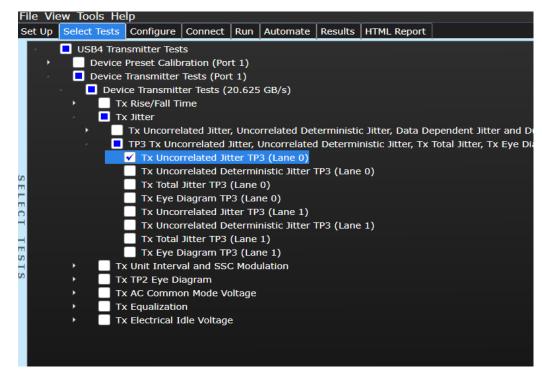

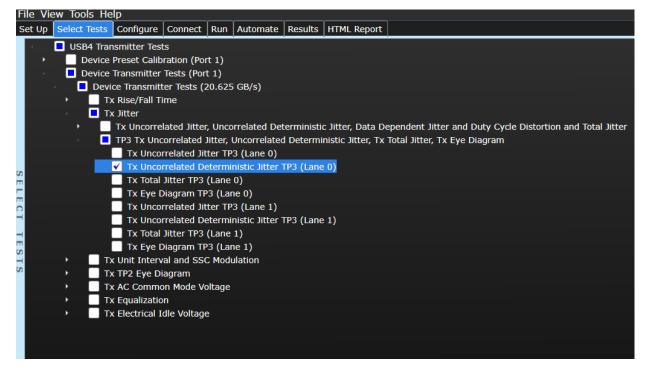

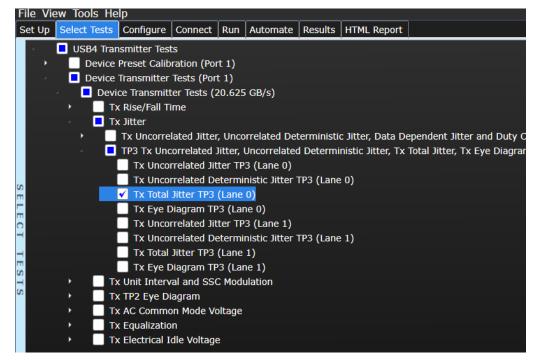

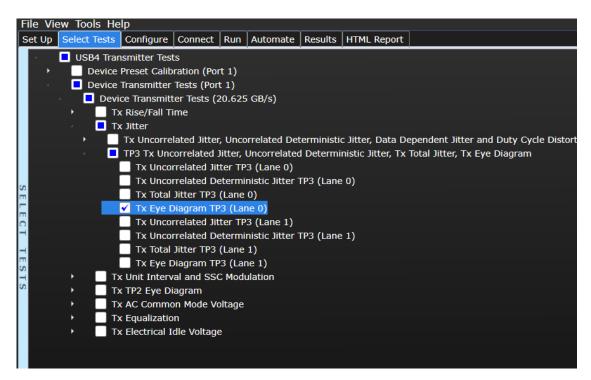

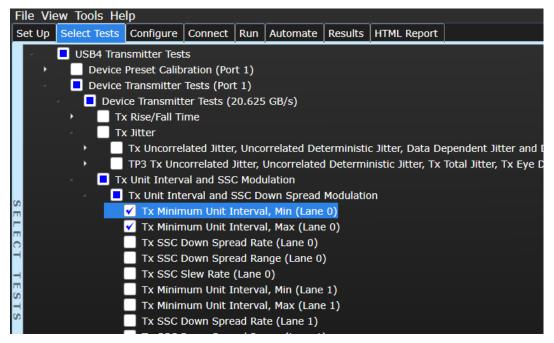

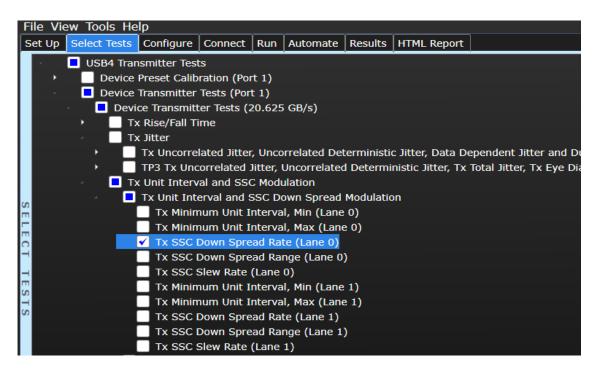

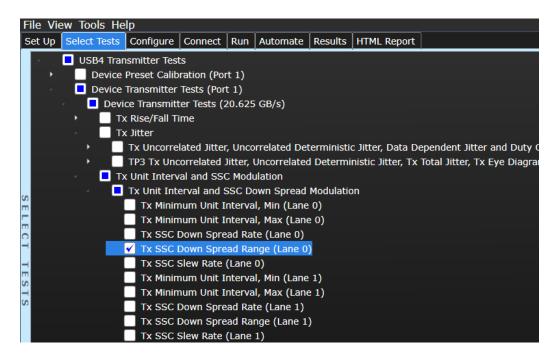

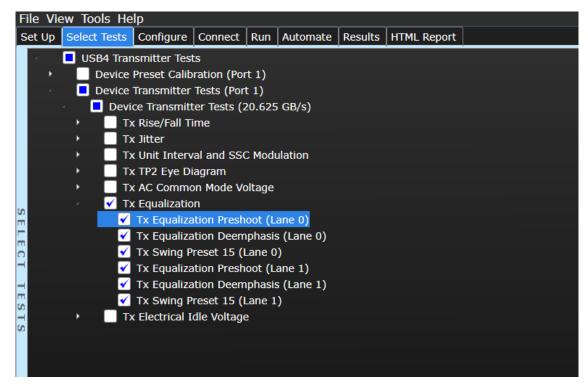

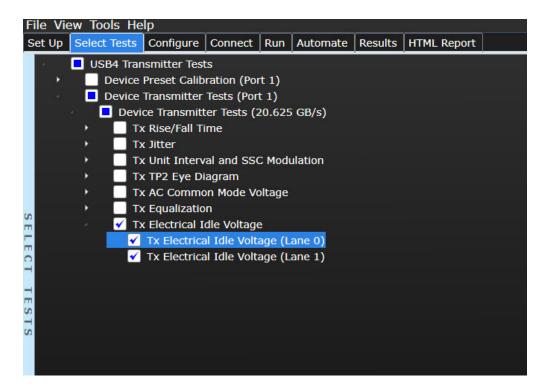

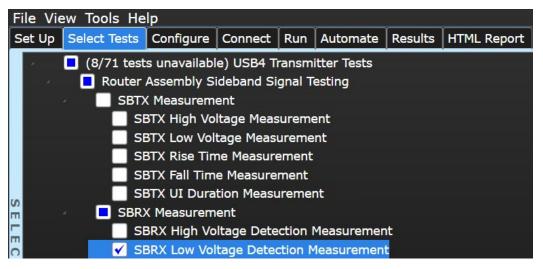

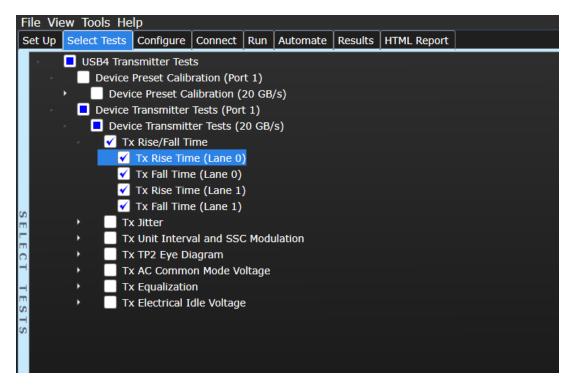

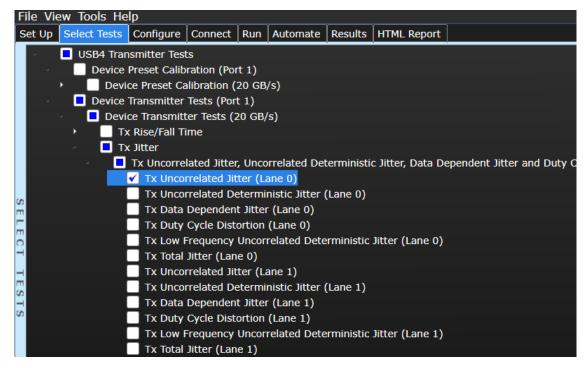

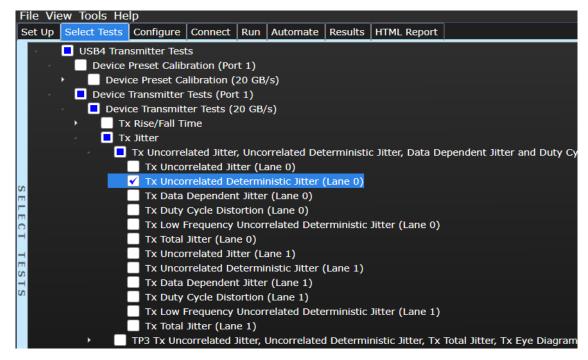

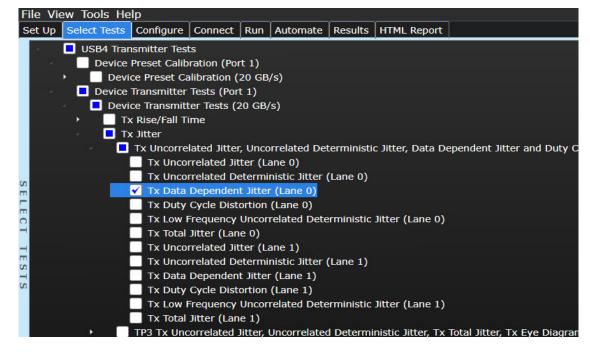

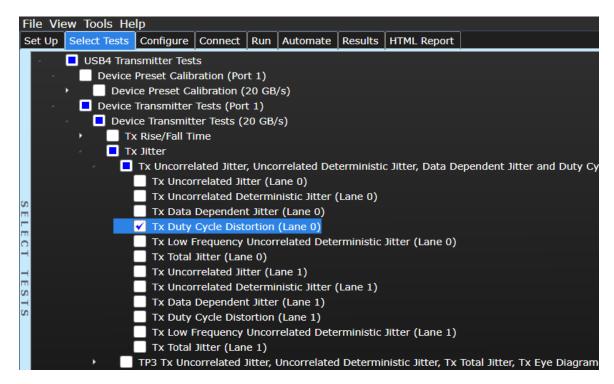

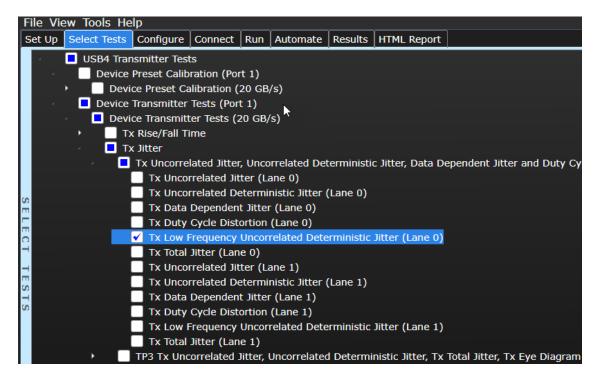

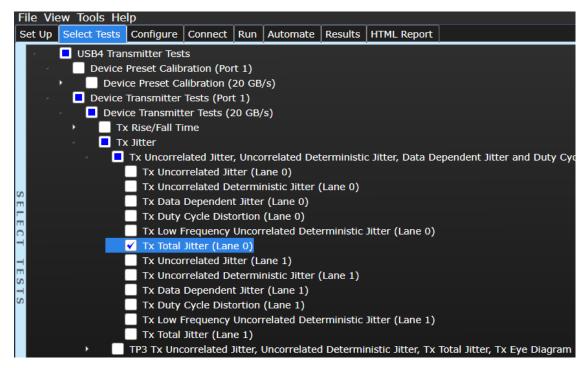

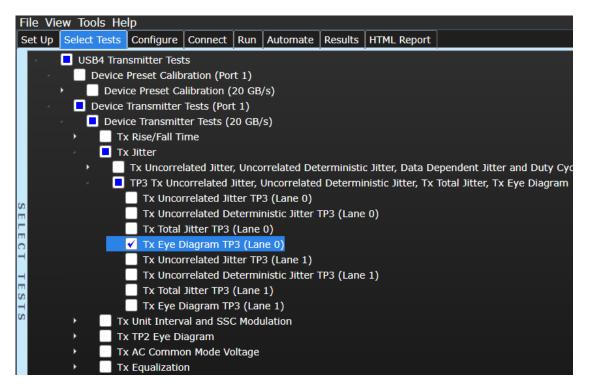

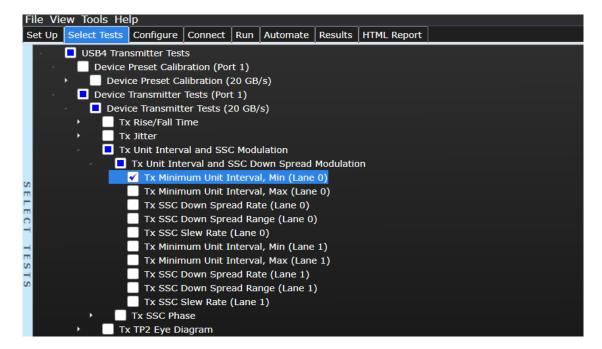

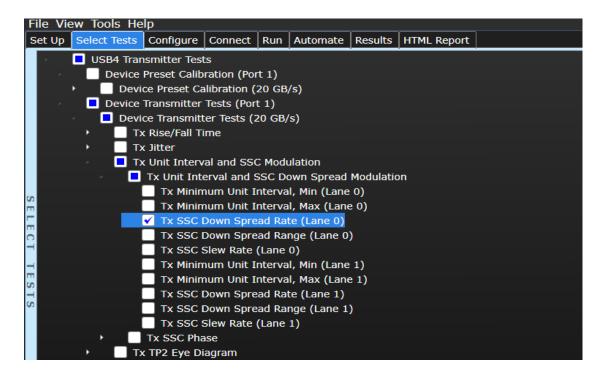

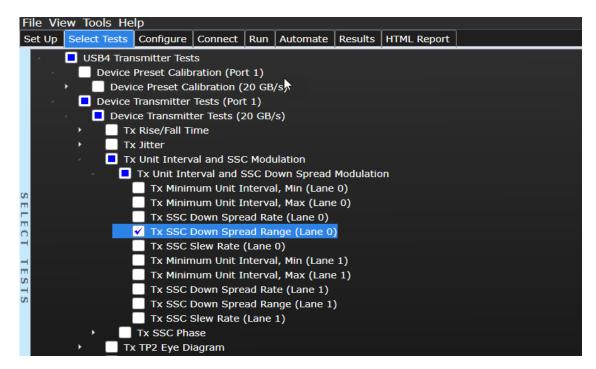

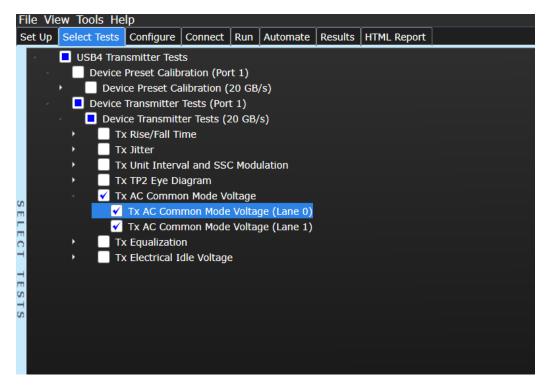

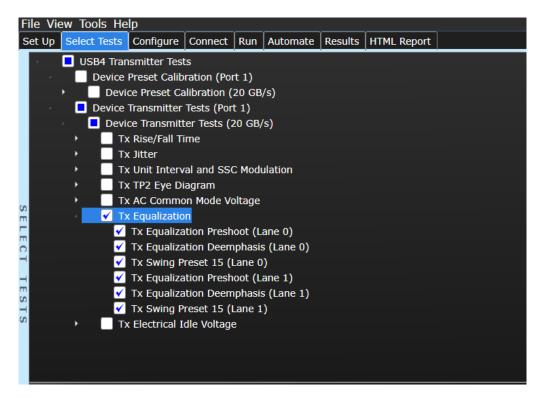

For example, Figure 8 shows how test groups are filtered when you select **Device Type:** as **Device**, **Number of Port** as **2 Ports** and **Test Lane:** as **Both lanes** along with selecting all bit rates. Similarly, Figure 9 shows how test groups are filtered when only one bit-rate is selected along with setting

**Device Type:** as **Host**, **Number of Port** as **1 Port** and **Test Lane:** as **Lane 0 only**. Select the tests that you want to run using the USB4 Test Application. Refer to the *Keysight D9040USBC USB4 Compliance Test Application Online Help* to know more about how to select tests.

NOTE

The **Test Lane** drop-down options in the **Set Up** tab, when the Test App is launched on a 4-Channel Oscilloscope, are different from that on a 2-Channel Oscilloscope. Therefore, on the latter instrument, only **Lane 0 only** or **Lane 1 only** options appear, as otherwise shown in Figure 8.

Figure 8 Selecting Transmitter Tests for all bit rates

Figure 9 Select Transmitter Tests for a single bit rate

NOTE

When running the Test App on a 2-Channel Oscilloscope, the **Select Tests** tab shall display tests pertaining to either **Lane 0 only** or to **Lane 1 only**.

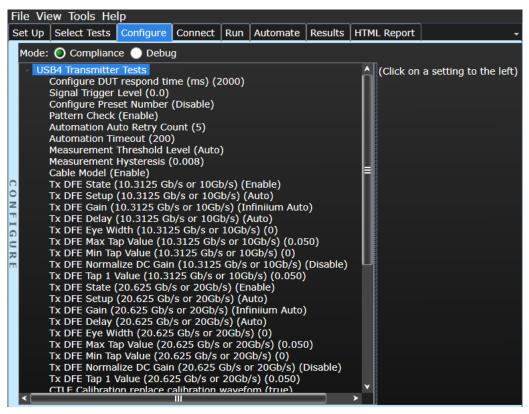

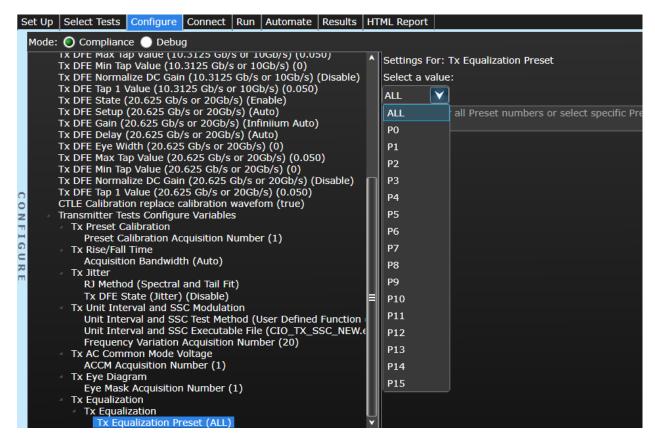

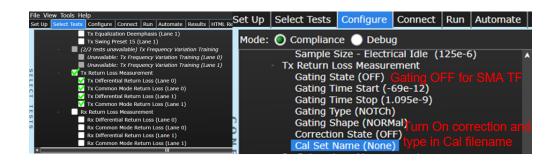

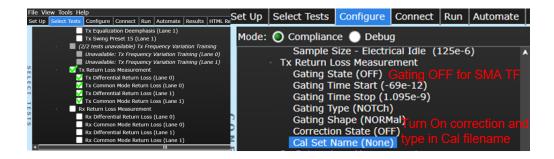

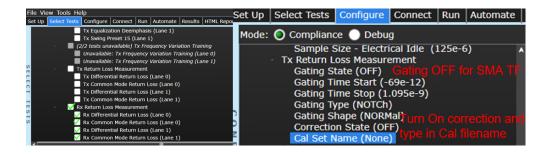

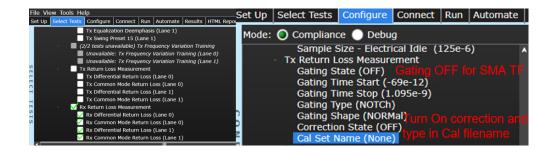

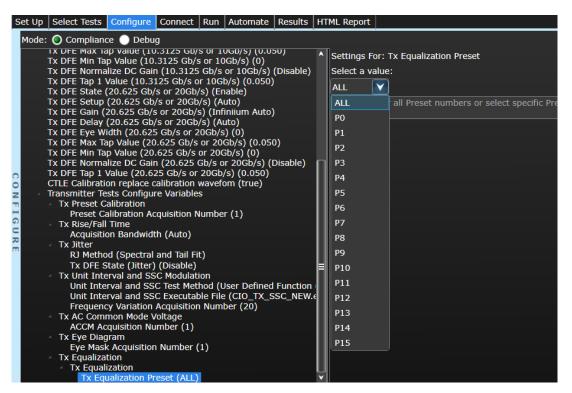

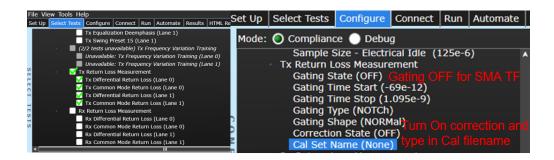

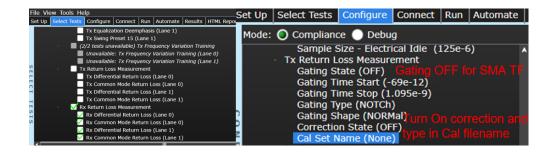

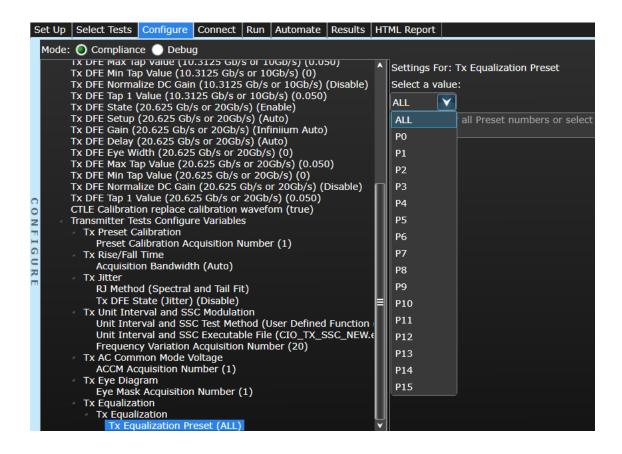

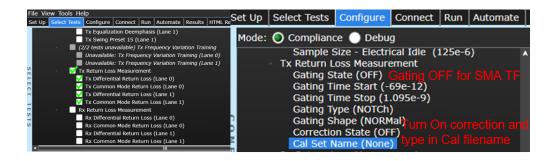

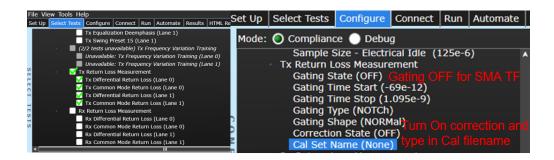

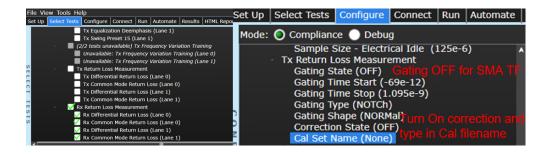

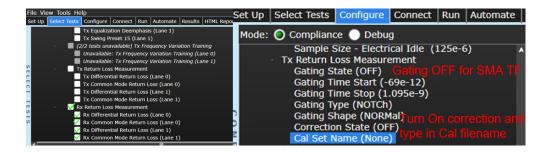

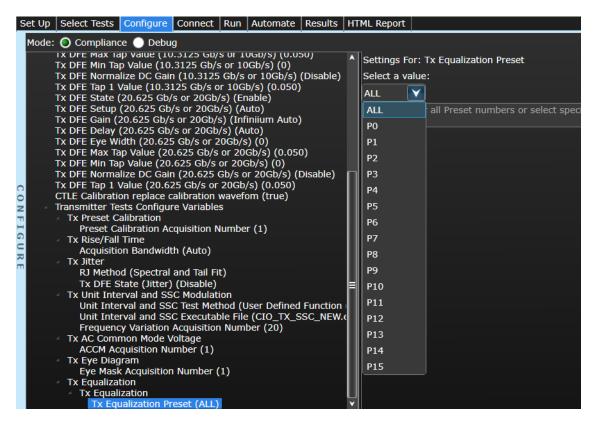

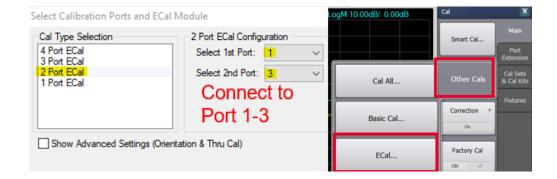

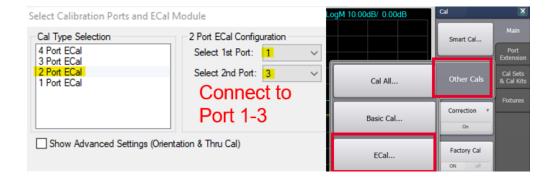

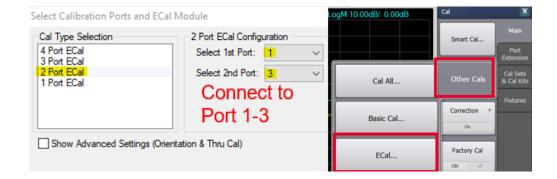

4 Under the **Configure** tab, you may modify the values for various configurable options associated with the compliance tests. By default, the USB4 Test Application sets the values of these options to the optimum value according to the standard specifications.

Figure 10 Configure options for USB4 Tests

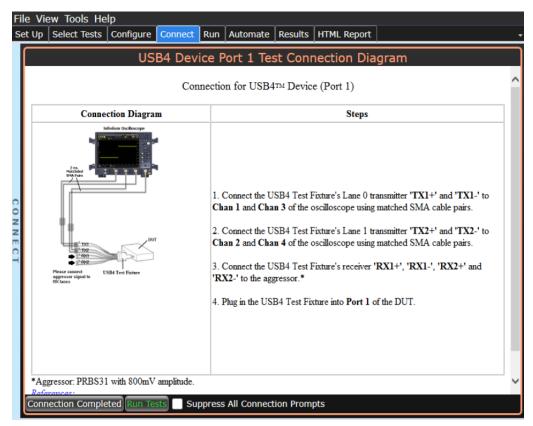

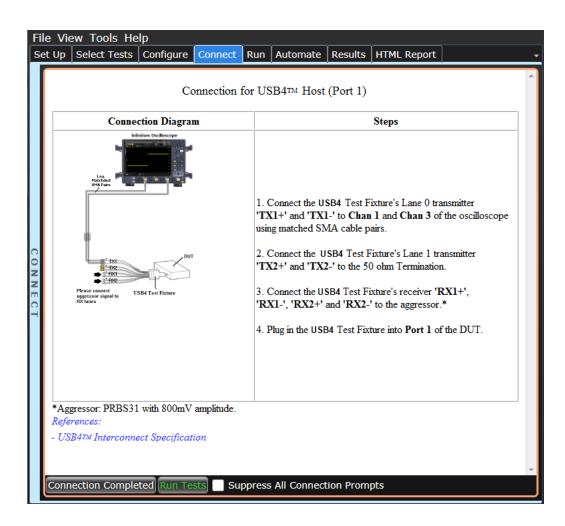

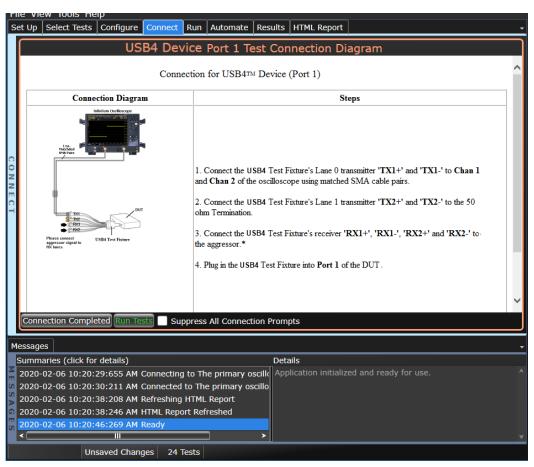

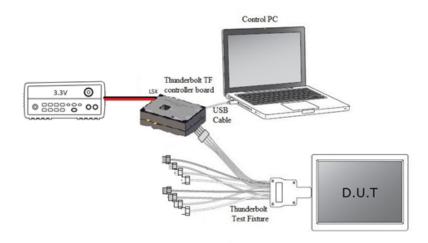

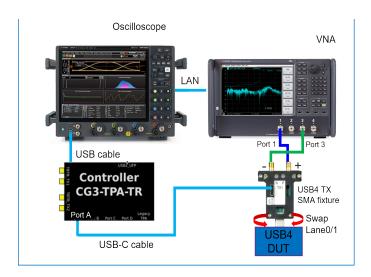

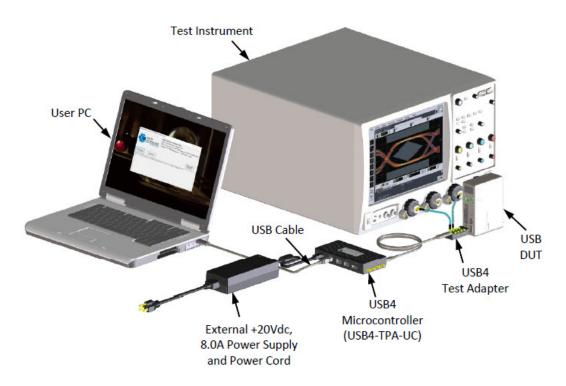

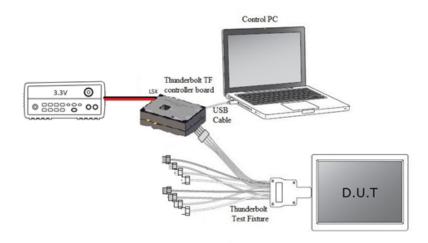

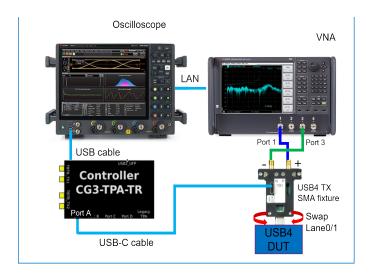

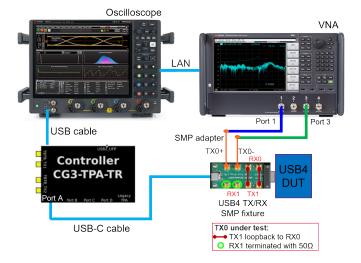

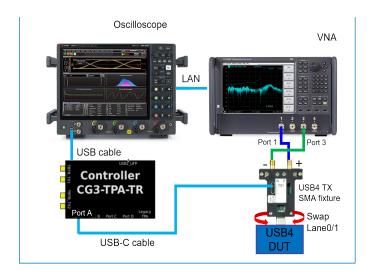

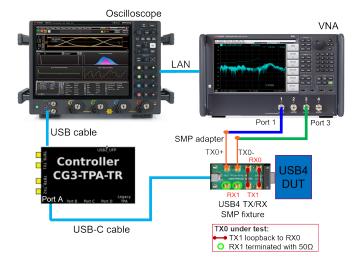

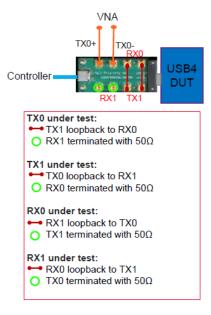

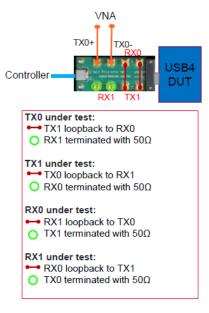

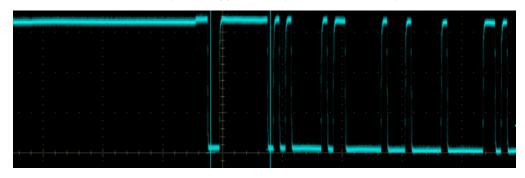

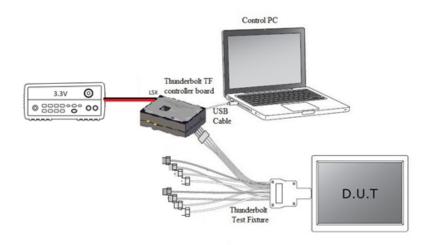

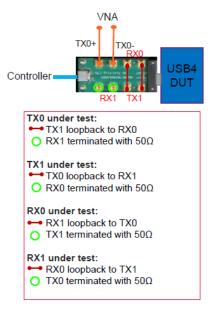

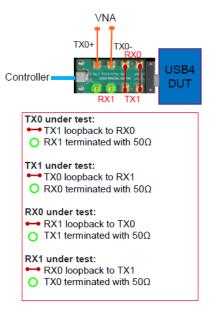

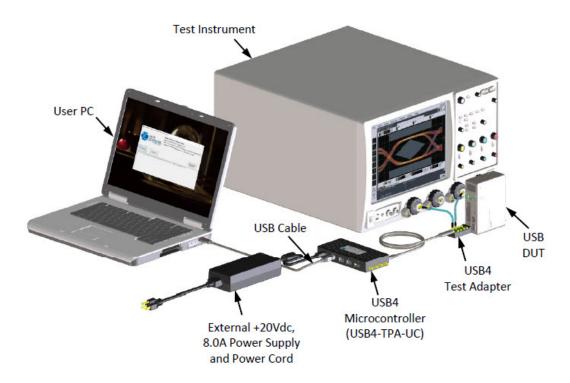

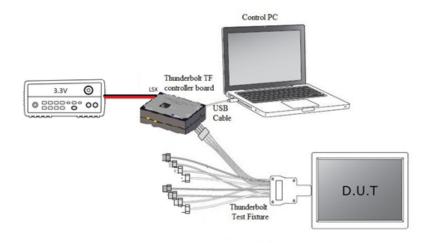

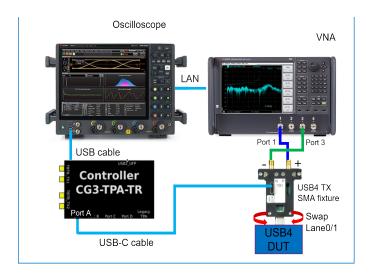

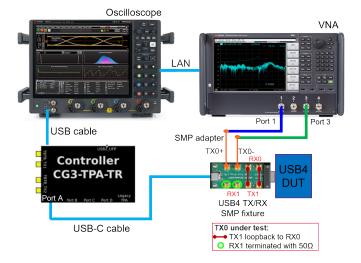

5 Under the **Connect** tab, the USB4 Test Application displays a Connection Diagram along with a list of instructions. Figure 11 and Figure 12 show the connection diagrams for a 2-Lane set up and for a 1-Lane set up, respectively, on a 4-Channel Oscilloscope, whereas Figure 13 shows the connection diagram for the "Lane 0 Only" set up on a 2-Channel Oscilloscope. If you have already set up a physical connection, you may verify else connect the DUT with the Oscilloscope as shown under this tab. Note that during some test runs, the application may prompt you for a change in physical connection/setup.

Figure 11 Connection Diagram and Instructions for a 2-Lane test set up on a 4-Ch Oscilloscope

Figure 12 Connection Diagram and Instructions for a 1-Lane test set up on a 4-Ch Oscilloscope

Figure 13 Connection Diagram and Instructions for "Lane 0 Only" on 2-Channel Oscilloscope

6 Once you have performed steps 1 to 5, you are ready to run compliance tests on the USB DUT. Additionally, you may configure/modify the run settings, automate options in the Test Application, view, export and print the test results and the HTML reports generated by the Test Application. Refer to the Keysight D9040USBC USB4 Compliance Test Application Online Help to know more about how to use the Test Application.

# Calibration Setup for Compliance Tests

Before running compliance tests on a USB DUT, it is imperative that the testing equipment and its accessories be calibrated. The USB4 Test Application provides the options to run Channel Skew Calibration and configure settings for Preset Calibration.

#### Channel Skew Calibration

In order to achieve accurate test results and to verify that the Device under test is compliant to the standards, it is necessary to calibrate the oscilloscope channels that are connected via cables to the USB DUT.

#### Perform the following:

1 In the Channel Skew Calibration area of the Set Up tab of the USB4 Test Application, click the Calibrate Setup button.

Figure 14 Channel Skew Calibration area under the **Set Up** tab

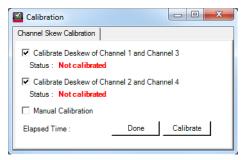

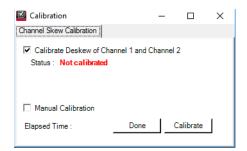

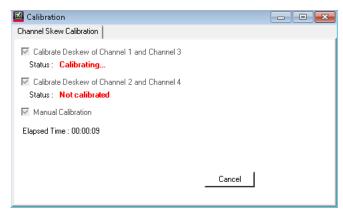

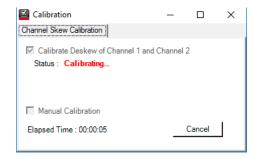

2 The **Calibration** window appears, where the **Channel Skew Calibration** tab is displayed by default, as shown in Figure 15 for a 4-Channel Oscilloscope and in Figure 16 for a 2-Channel Oscilloscope.

Figure 15 Options for Channel Skew Calibration on a 4-Channel Oscilloscope

Figure 16 Options for Channel Skew Calibration on a 2-Channel Oscilloscope

Under the **Channel Skew Calibration** tab, the USB4 Test Application displays the status of the oscilloscope channels that have been calibrated for de-skew. As shown in the images above, the options are checked by default and the status of each of these options is **Not Calibrated**. You may also select the **Manual Calibration** check box to perform Channel Skew Calibration later.

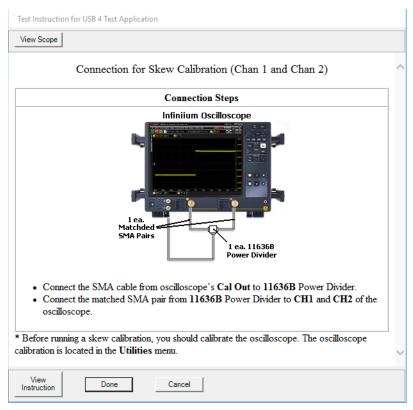

To start Calibration of the selected Oscilloscope channel pairs, click the **Calibrate** button. The **Test Instruction for USB4 Compliance** window appears.

Figure 17 Instructions for Channel Skew Calibration for the selected Channels on a 4-Ch Oscilloscope

Figure 18 Instructions for Channel Skew Calibration for the selected Channels on a 2-Ch Oscilloscope

The **Test Instruction for USB4 Compliance** window provides instructions and connection diagram required to be set up to perform Channel Skew Calibration. Note that before you start performing Channel Skew Calibration, the oscilloscope must have been calibrated.

On the Test Instruction for USB4 Compliance window,

- Click the **View Scope** button to minimize this window and to see the oscilloscope screen for the waveform and to use the Infiniium controls to perform oscilloscope calibration (if it has not been done yet).

- 2 Click the **View Instruction** button to maximize the window to view the instructions and the connection diagram again.

- 3 Once you have set up the physical connection for Channel Skew Calibration for the respective channels, click **Done** to begin Calibration. You may click **Cancel** at any point to simply return to the **Calibration** window.

When you click **Done**, the **Calibration** window displays again with the updated Status along with the time elapsed during this process, as shown in Figure 19 and Figure 20.

Figure 19 Changes in Calibration status on a 4-Channel Oscilloscope

Figure 20 Changes in Calibration status on a 2-Channel Oscilloscope

Once the Calibration process is successfully completed, the status changes to **Calibrated**. You may click **Cancel** to stop the process of Channel Skew Calibration at any time.

4 After the Channel Skew Calibration is complete, click the **Done** button to return to the USB4 Test Application Test Environment Setup.

#### 3

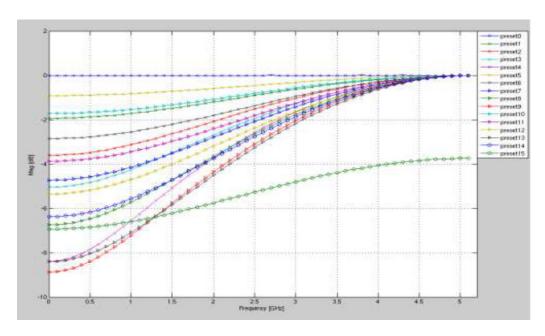

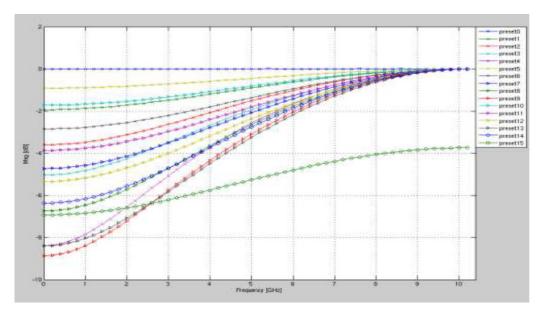

#### **Preset Calibration**

The **Preset Calibration** tab allows you to select the preset number, which has been set on the USB DUT, to be used in the USB4 Test Application. You may also perform the preset sweep to find the optimum preset.

#### Perform the following:

1 In the **Test Setup** area of the **Set Up** tab of the USB4 Test Application, click the **Test Setup** button.

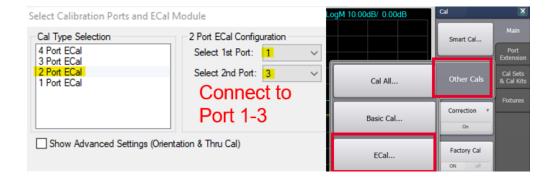

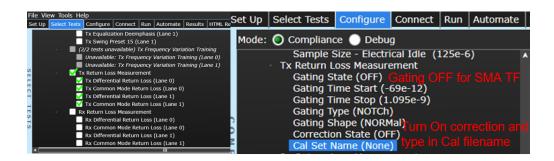

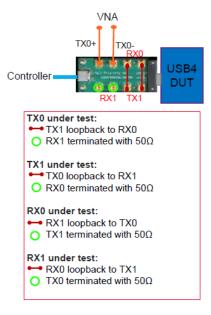

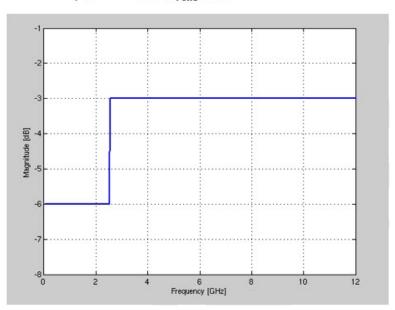

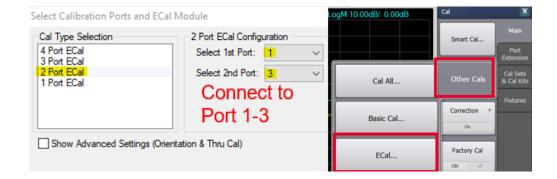

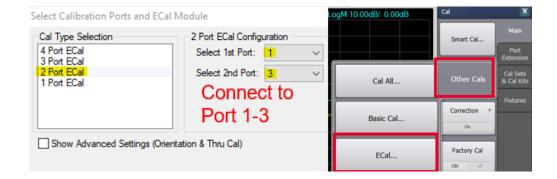

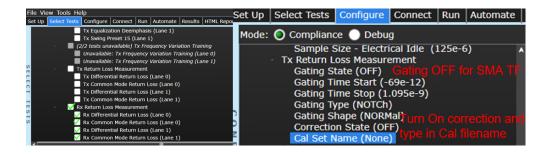

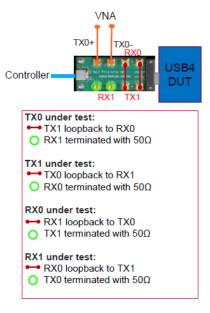

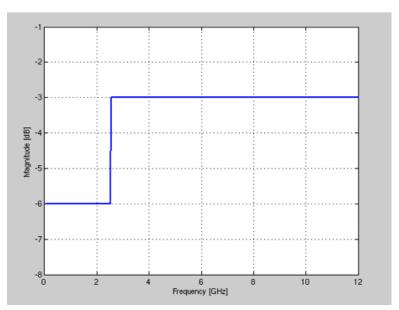

Figure 21 Test Setup area under the **Set Up** tab